# NEW TECHNIQUES FOR PARALLEL SIMULATION OF DEVS AND CELL-DEVS MODELS IN CD++

By

Ezequiel Glinsky, B. Sc.

A thesis submitted to

The Faculty of Graduate Studies and Research

In partial fulfillment of

the requirements of the degree of

Master of Applied Science

Ottawa-Carleton Institute for Electrical and Computer Engineering

Department of Systems and Computer Engineering

Carleton University

Ottawa, Ontario

Canada

© Copyright 2004, Ezequiel Glinsky

The undersigned hereby recommends to the Faculty of Graduate Studies and Research

acceptance of the thesis

### New techniques for parallel simulation

### of DEVS and Cell-DEVS models in CD++

Submitted by Ezequiel Glinsky

In partial fulfillment of the requirements for the

Degree of Master of Applied Science

Thesis Supervisor

Dr. Gabriel Wainer

Chair, Department of Systems and Computer Engineering

Dr. Rafik A. Goubran

**Carleton University**

2004

### ABSTRACT

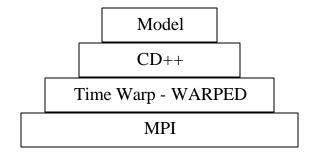

DEVS is a sound formal modeling and simulation (M&S) framework based on generic dynamic system concepts. Cell-DEVS is a formalism for cell-shaped models based on DEVS. This work presents a new simulation technique for execution of DEVS and Cell-DEVS models in distributed environments. The parallel simulator is based on Time Warp, an optimistic synchronization protocol, and developed as a new simulation engine for CD++, a M&S toolkit that implements DEVS and Cell-DEVS theory. The presented technique uses a non-hierarchical approach that simplifies the structure of the simulator and reduces the communication overhead. In order to analyze the performance of our simulator, we introduce a synthetic benchmark to test DEVS-based simulators. The performance analysis shows reasonable overhead in comparison to other simulators. Using a distributed environment, our simulator outperforms other alternatives and achieves considerable speedups.

### ACKNOWLEDGMENTS

I want to start by thanking my supervisor, Prof. Gabriel Wainer, for his support and guidance over the last years. Working with him has been a challenging yet rewarding experience.

I am grateful to several people at Carleton University who helped me in many ways, especially to Diane Berezowski, Laura Cohen, and Luc Lalande.

I have had a wonderful time with friends at the Graduate Students' Association. I will always keep those people, those moments, and that organization in my heart. In particular, I want to thank my dream team: Cathy Anstey, Glen Bornais, Robert Johnson, Phil Robinson, and Andrea Rounce.

Thanks to those who became my closest family in Canada. My biggest gratitude goes to Juanca and Leo for our *café mirón* and our Argentinean friendship, and to my favourite Chilean, Loreto. I am very grateful to many friends I met in Ottawa, especially to Abeer, the Martino family, Thierry, José Merseguer and my unforgettable *rumis* Nestor and Covy.

I am thankful to my dearest friends in Argentina: Alberto Siless, Leandro Resnik, Lisandro Icardi, Luciano Tirantte, Martin Dragovetzky, Patricio Donato, and their partners.

I love and admire my parents, Isabel Monzón and Gregorio Glinsky. I carry their love, support and encouragement as a gift. Thanks to my brothers, Adrian and Fernando, who are always with me.

This thesis is dedicated to the love of my life, Solange Epelman.

# TABLE OF CONTENTS

|                                                                                                                 | Page                  |

|-----------------------------------------------------------------------------------------------------------------|-----------------------|

| ABSTRACT                                                                                                        |                       |

| ACKNOWLEDGMENTS                                                                                                 | IV                    |

| LIST OF TABLES                                                                                                  | VII                   |

| LIST OF FIGURES                                                                                                 | VIII                  |

| LIST OF ACRONYMS                                                                                                | XI                    |

| CHAPTER 1: INTRODUCTION                                                                                         | 1                     |

| 1.1 Contribution                                                                                                |                       |

| 1.2 Thesis Organization                                                                                         |                       |

| CHAPTER 2: DISCRETE EVENT MODELING AND SI                                                                       | MULATION              |

| TECHNIQUES 12                                                                                                   |                       |

| 2.1 DEVS and Parallel DEVS formalisms                                                                           |                       |

| 2.2 Modeling Cell Spaces                                                                                        |                       |

| 2.3 DEVS-based toolkits for M&S                                                                                 |                       |

| 2.4 The CD++ toolkit                                                                                            |                       |

| 2.5 Parallel and Distributed Simulation                                                                         |                       |

| <ul><li>2.5.1 Conservative Simulation</li><li>2.5.2 Optimistic Simulation</li><li>2.6 The Warped tool</li></ul> |                       |

| CHAPTER 3: ENABLING NEW TECHNIQUES FOR PA                                                                       | ARALLEL SIMULATION    |

| OF DEVS AND CELL-DEVS MODELS                                                                                    |                       |

| CHAPTER 4: OPTIMISTIC PDES OF DEVS MODELS .                                                                     |                       |

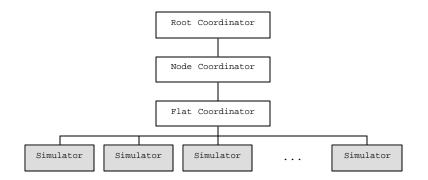

| 4.1 Hierarchical and Flat Simulation in CD++                                                                    |                       |

| 4.2 Algorithms for Parallel and Distributed Simulation using                                                    | ng a Flat Approach 66 |

| <ul><li>4.2.1 Simulator</li><li>4.2.2 Flat Coordinator</li><li>4.2.3 Node Coordinator</li></ul>                 |                       |

|               | Coordinator<br>Scenarios             |     |

|---------------|--------------------------------------|-----|

|               | IMPLEMENTING THE ABSTRACT SIMULATORS |     |

| 5.1 Execution | of DEVS and Cell-DEVS models         |     |

| CHAPTER 6:    | PERFORMANCE ANALYSIS                 | 107 |

| 6.1 DEVStone  | ,                                    | 107 |

| 6.2 Performan | ce Analysis for DEVS models          | 113 |

| 6.3 Performan | ce Analysis for Cell-DEVS models     |     |

| CHAPTER 7:    | CONCLUSIONS                          |     |

| 7.1 Future Wo | ork                                  | 141 |

| REFERENCES    |                                      |     |

## LIST OF TABLES

|                                | Page |

|--------------------------------|------|

| Table 1: Simulation parameters |      |

## **LIST OF FIGURES**

| Pag                                                                               | ge |

|-----------------------------------------------------------------------------------|----|

| Figure 1: Basic entities in M&S and their relationships [Zei00]                   | 2  |

| Figure 2: DEVS semantics                                                          | 14 |

| Figure 3: Sketch of a cellular automaton [Wai00]                                  | 20 |

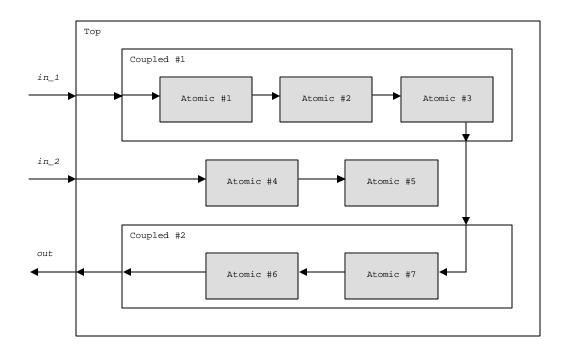

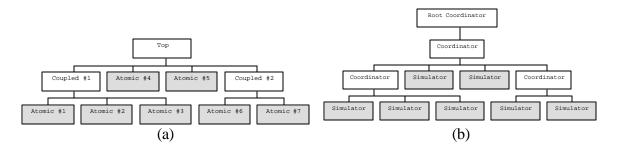

| Figure 4: CD++ (a) Model hierarchy, (b) Processor hierarchy                       | 28 |

| Figure 5: Diagram of atomic model Controller Unit                                 | 31 |

| Figure 6: Specification of atomic model Controller Unit in CD++ (part 1)          | 33 |

| Figure 7: Specification of atomic model Controller Unit in CD++ (part 2)          | 34 |

| Figure 8: Diagram of the coupled model AMS                                        | 35 |

| Figure 9: Specification of coupled model AMS in CD++                              | 36 |

| Figure 10: Specification of Cell-DEVS model life in CD++                          | 37 |

| Figure 11: Automated Manufacturing System partitioned in two LPs                  | 40 |

| Figure 12: Violation of local causality constraint in a distributed simulation    | 41 |

| Figure 13: Structure of LPs and simulation objects in Warped [Mar96]4             | 48 |

| Figure 14: Summary of Warped API [Mar97]                                          | 49 |

| Figure 15: Layered architecture of the CD++ optimistic simulator                  | 56 |

| Figure 16: New processors' class hierarchy in CD++                                | 57 |

| Figure 17: Layout of a sample DEVS model                                          | 59 |

| Figure 18: Sample DEVS model in hierarchical CD++ (a) models, and (b) processors5 | 59 |

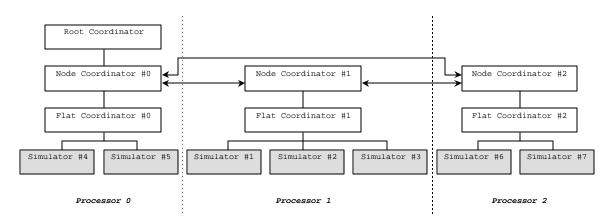

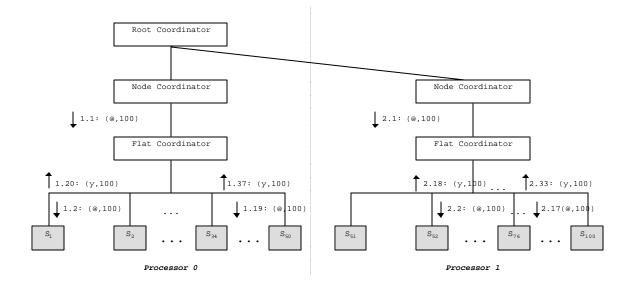

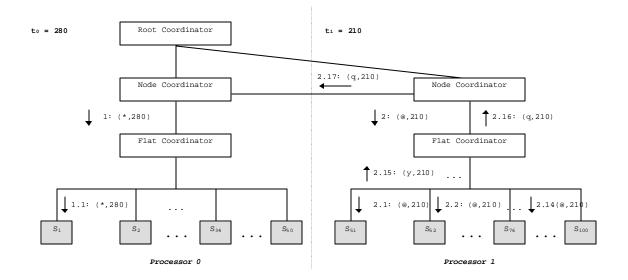

| Figure 19: Processor hierarchy using a flat approach                              | 51 |

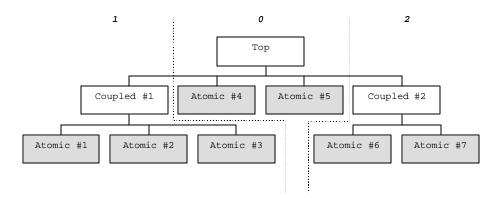

| Figure 20: Model partitioned in three blocks                                      | 52 |

| Figure 21: Model partition file for CD++                                          | 53 |

| Figure 22: Distributed processor structure for partitioned model                  | 53 |

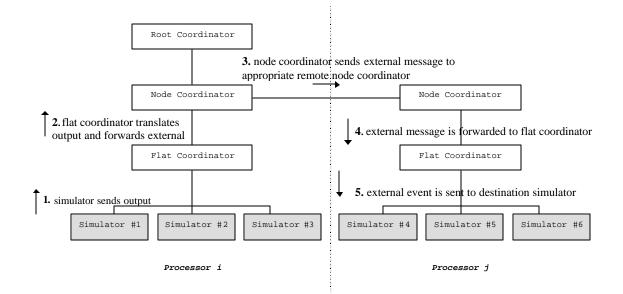

| Figure 23: Sending an output to a remote simulator                                | 56 |

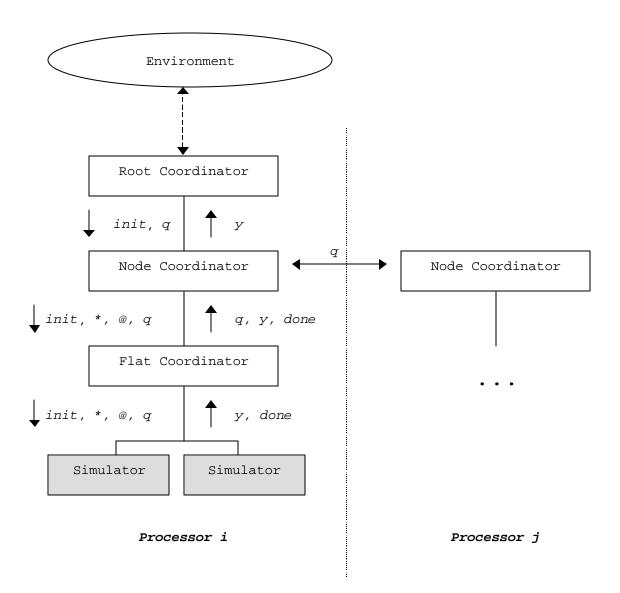

| Figure 24: Message flow in a distributed simulation of DEVS and Cell-DEVS         | 79 |

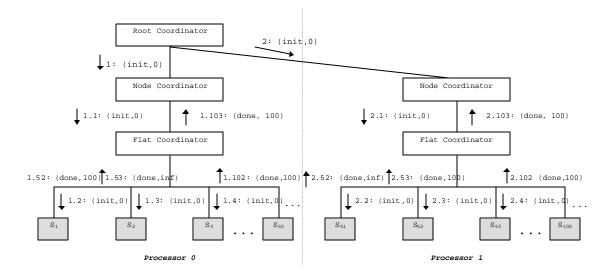

| Figure 25: Initialization phase in sample Cell-DEVS model                         | 31 |

| Figure 26: Collect phase in sample Cell-DEVS model                                    |

|---------------------------------------------------------------------------------------|

| Figure 27: Straggler message received during the simulation of a Cell-DEVS model84    |

| Figure 28: Reception of a straggler message in a <i>node coordinator</i>              |

| Figure 29: State of the <i>node coordinator</i> after the rollback                    |

| Figure 30: Some classes of the Warped API [Mar97]                                     |

| Figure 31: UML class diagram for the new DEVS processors91                            |

| Figure 32: Class diagram for messages in CD++94                                       |

| Figure 33: Classes LogicalProcess and ParallelMainSimulator96                         |

| Figure 34: Sample CD++ event file                                                     |

| Figure 35: <i>flat coordinator</i> log file for a sample Cell-DEVS model (partial)100 |

| Figure 36: <i>simulator</i> log file for cell model <i>life(0,2)</i> (partial)103     |

| Figure 37: <i>simulator</i> log file for a sample atomic model (partial)104           |

| Figure 38: node coordinator log file (partial)104                                     |

| Figure 39: Sample output file for a DEVS model105                                     |

| Figure 40: Example of a LI model: (a) top level; (b) level 4110                       |

| Figure 41: Model file generated by DEVStone for a LI model110                         |

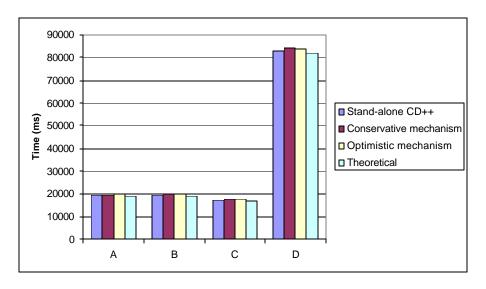

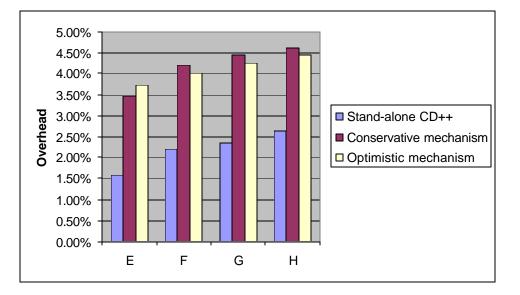

| Figure 42: Execution times for LI models in a single CPU using the optimistic         |

| parallel simulator and other simulation engines116                                    |

| Figure 43: Overhead incurred by the optimistic parallel simulator and other           |

| simulation engines for LI models116                                                   |

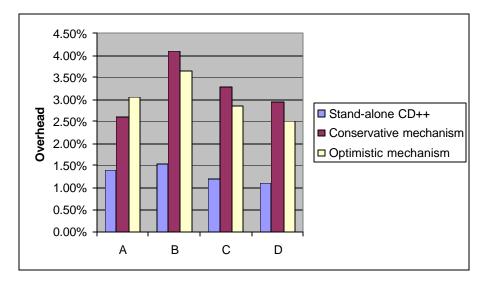

| Figure 44: Execution times for HI models in a single CPU using the optimistic         |

| parallel simulator and other simulation engines119                                    |

| Figure 45: Overhead incurred by the optimistic parallel simulator and other           |

| simulation engines for HI models119                                                   |

| Figure 46: Execution times for HO models in a single CPU using the optimistic         |

| parallel simulator and other simulation engines120                                    |

| Figure 47: Overhead incurred by the optimistic parallel simulator and other           |

| simulation engines for HO models121                                                   |

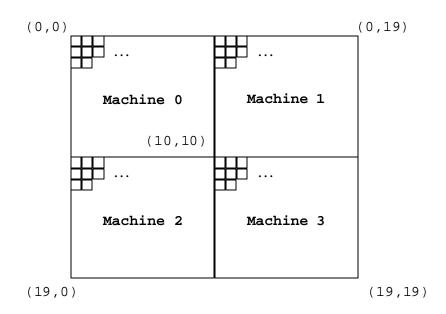

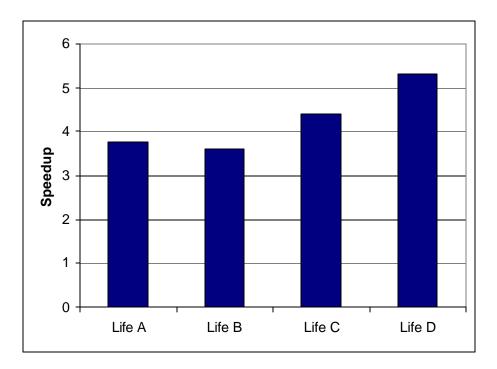

| Figure 48: Specification of Cell-DEVS model life in CD++                              |

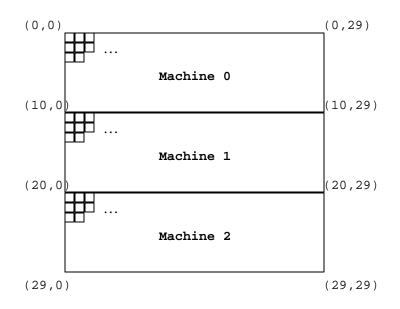

| Figure 49: Partition of 20x20 life model in 4 machines                           |

|----------------------------------------------------------------------------------|

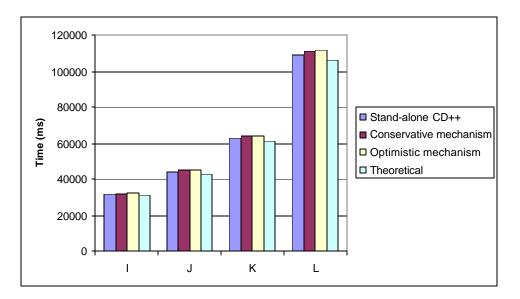

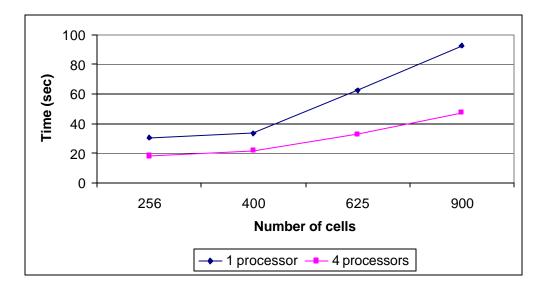

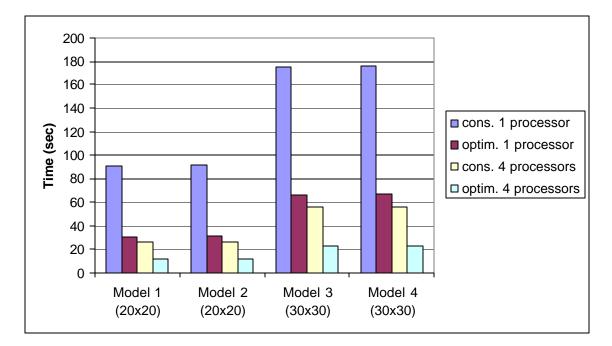

| Figure 50: Execution times for life model (1 vs. 4 processors)126                |

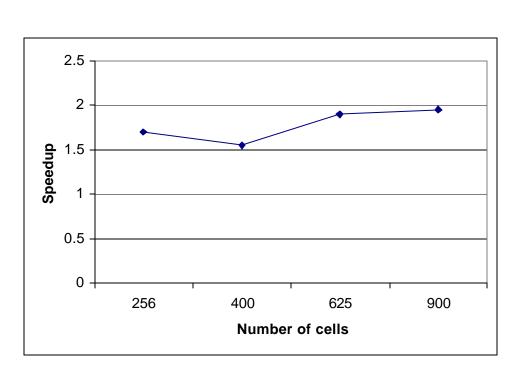

| Figure 51: Execution speedups for life model running in 4 processors128          |

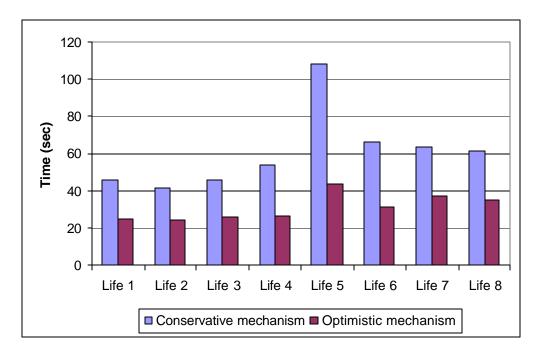

| Figure 52: Execution times for life model using optimistic and conservative      |

| simulators in 4 processors                                                       |

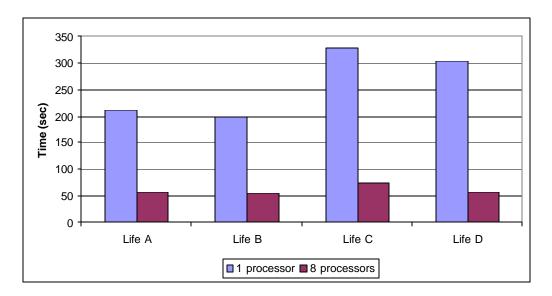

| Figure 53: Execution times for 50x50 life model in 1 and 8 processors130         |

| Figure 54: Execution speedups for 50x50 life model running in 8 processors131    |

| Figure 55: A different partition strategy for the life model                     |

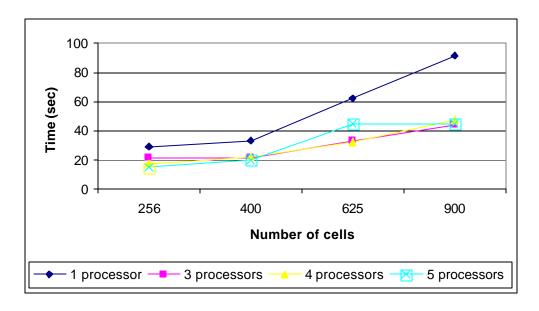

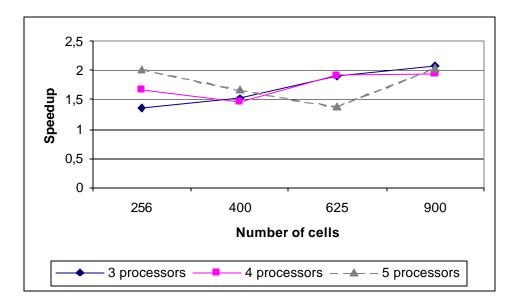

| Figure 56: Execution times for life model using 1, 3, 4 and 5 processors133      |

| Figure 57: Speedups for life model distributed in 3, 4 and 5 processors134       |

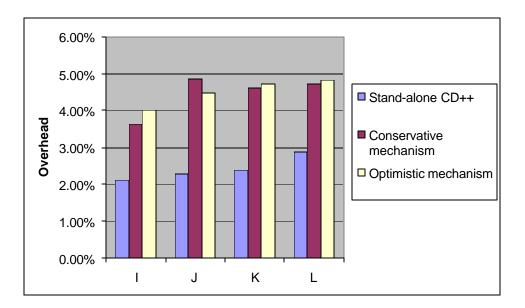

| Figure 58: Execution times for Cell-DEVS model using conservative and optimistic |

| simulators in 1 and 4 processors                                                 |

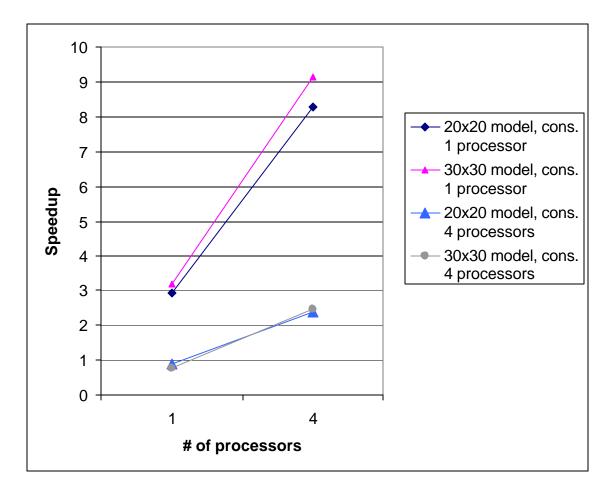

| Figure 59: Speedup obtained by the optimistic simulator in 1 and 4 processors136 |

# LIST OF ACRONYMS

| AMS    | Automatic Manufacturing System               |

|--------|----------------------------------------------|

| API    | Application Program Interface                |

| CORBA  | Common Object Request Broker Architecture    |

| CVDS   | Continuous Variable Dynamic Systems          |

| DEDS   | Discrete Event Dynamic Systems               |

| DEVS   | Discrete Event System Specification          |

| GVT    | Global Virtual Time                          |

| HLA    | High Level Architecture                      |

| LP     | Logical Process                              |

| M&S    | Modeling and Simulation                      |

| MPI    | Message Passing Interface                    |

| OMG    | Object Management Group                      |

| PDES   | Parallel Discrete Event Simulation           |

| P-DEVS | Parallel Discrete Event System Specification |

| UML    | Unified Modeling Language                    |

### **Chapter 1: INTRODUCTION**

Modeling and simulation (M&S) methodologies have become essential for understanding, analyzing and developing a wide variety of systems. In the last centuries scientists and engineers have relied on the use of models to describe the properties of the systems under study. Most of these models were defined with mathematical representations, allowing mathematical analysis techniques. Nevertheless, these methods are unsuitable for many complex artificial applications developed in the last 50 years, such as traffic control systems, automated factories, computer architectures, or biomedical devices. These methods are not appropriate for studying various natural systems either, especially when the complexity or the required level of detail is high.

The development of computers has offered alternative methods; models can be executed using computer simulation, allowing users to experiment different conditions under risk-free environments. M&S is also frequently used for training and educational purposes, using models previously developed by experts within an application domain. Nowadays, M&S is a well-developed, well-proven approach to problem solving, which advances steadily as more computing power becomes available at less cost.

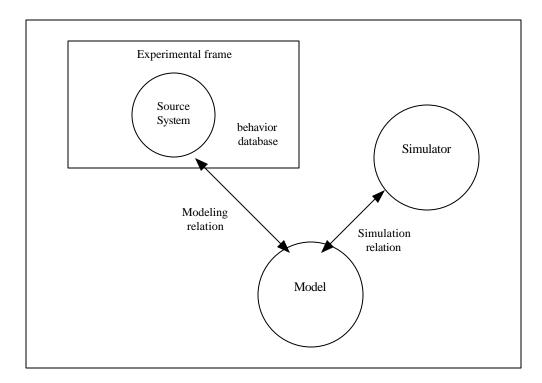

The M&S process begins with a problem that needs to be solved or understood. Figure 1 shows the basic entities in M&S and their relationships, as described in [Zei00]:

Figure 1: Basic entities in M&S and their relationships [Zei00]

The **source system** is the environment under analysis. The elements observed in the system and the conditions under which the system is observed establish the **experimental frame**. A **model** is an abstract representation of such system that is constructed using the acquired data. Generally, a model includes a set of instructions, rules, or mathematical equations to duplicate the behaviour of the actual system. A **simulator** is an agent capable of executing the model's instructions, and thus generating the model's behavior.

Figure 1 shows the two fundamental relationships that connect the basic entities. The **modeling relation** links the real system and the experimental frame with the model in terms of validity. It is concerned with how well the model behaviour agrees with the system behaviour under the conditions specified in the experimental frame. The **simulator relation** links a model and a simulator. This relation deals with how faithfully the simulator executes the instructions of the model.

The separation between model and simulator enables to validate the model and to verify the correctness of the simulator independently [Zei99b]. This distinction results in simulation algorithms whose correctness has been rigorously established separately from the model.

Nowadays, several formalisms coexist and are being used to model and simulate different types of systems. In this work, we focus on the **DEVS** (Discrete Events systems Specification) formalism [Zei76, Zei00], which has been proven to be a universal formalism to represent **DEDS** (Discrete Event Dynamic Systems). DEVS was originally defined in the 1970's as a discrete-event M&S mechanism. DEVS is a sound formal framework based on generic dynamic systems concepts that supports provably correct, efficient, event-based simulation. The framework enables the construction of models in a hierarchical, modular fashion, allowing component reuse and reducing development and testing time. **Parallel DEVS** or **P-DEVS** [Cho94a] is an extension to DEVS that provides a better way to handle simultaneously scheduled events, while keeping all the major properties of the original formalism. Since P-DEVS eliminates serialization constraints existing in the original DEVS formalism, it enables more efficient execution of models in parallel and distributed environments.

The **Timed Cell-DEVS** formalism [Wai98] combines cellular automata [Wol86] with DEVS theory, allowing individual cells to be defined as basic DEVS models and

coupled together to form complete cell spaces. The formalism supports the definition of complex cell behavior with simple constructions.

Numerous tools that implement these formalisms have been used in a variety of industries and areas of expertise, including chemistry, biology, computer architectures, telecommunication networks, decision support systems, military applications, and transportation. CD++ [Wai02] is a M&S tool that implements DEVS and Cell-DEVS theory. CD++ was revised and extended several times, and it currently supports standalone [Rod99], real-time [Gli02a], and conservative parallel simulation [Tro01a]. CD++ has been used to model a variety of applications. The propagation of forest fires has been simulated with CD++ [Ame01] using a Cell-DEVS model. Environmental and vegetation conditions determine spread and intensity of fire. Three main groups of parameters are specified: vegetation type (caloric content, mineral content and density), fuel properties (the type of vegetation is classified according to its size), and environmental parameters (wind speed, humidity and field slope). External factors are taking into consideration for the spread of the fire in the region, such as the influence of rain or the activity of firefighters. The movement of robots in an industrial plant has also been studied with CD++ [Ame01]. Robots follow predefined one-way routes at a given speed with the risk of colliding with other robots, in which case they apply a strategy to continue their way. When a robot reaches its destination, the carried load is delivered and the robot is taken off the floor. In this application, a DEVS component adds new robots to the simulation. CD++ was used to study a watershed using Cell-DEVS [Ame01], based on a model previously defined in [Zei96]. The equations that define the filtration of water through

each layer of the soil were used to specify the rules of the Cell-DEVS model. The simulation allows the study of the accumulation of water on a region after a period of rain. A computer processor was simulated using a DEVS model defined in CD++ [Wai01]. This model includes the specification of components such as memory, registers, and control unit. The reproduction of a marine germ was studied with CD++ [Ame03]. The concentration of bacteria over time was simulated using a Cell-DEVS model. The variation of temperature was simulated using a DEVS model. The behavior of ants also been studied with CD++ [Ame03]. The model analyzes how ants find an existing source of food and carry the food back to the anthill. CD++ has been used to study the movement of crowds in a metro station [Ame03]. The model shows how people try to reach the doors of a railroad car. It also shows the conflict when they collide with people trying to get out from the railroad car. Modeling and simulation of urban traffic has been studied using ATLAS [Dia01]. ATLAS is a specification language to study the flow of vehicles in a city, which gives modelers a simple means to describe intersections, streets, and other constructions, such as railways, traffic lights and parking spaces. The flow of cars and trucks was studied in detail in [Dav00a].

M&S has become a fundamental tool in a wide variety of fields. As a result, many of the simulated systems are becoming more and more sophisticated. As these systems become larger and more complex, the resources provided by a single-processor machine become, in many cases, insufficient to execute those systems. **Parallel and distributed simulation** (PADS) deals with the issues introduced by distributing simulations over multiple processors. **Parallel discrete event simulation** (PDES) studies the execution of discrete event models in parallel or distributed computers. A PDES simulation advances by the occurrence of events that take place at discrete points in time. Fujimoto identified three major research communities involved in the field of parallel and distributed simulation [Fuj01]. The first group is the high performance computing community, whose work started in the late 1970's and 1980's. This group's main concern was to reduce execution time of applications by using multiple processors. Several synchronization algorithms developed by this community, such as Chandy-Misra-Bryant [Bry77, Cha79] and Time Warp [Jef85], introduced fundamental ideas that are still being applied. The second group is the defense community, mainly interested in integrating separate training simulations to facilitate interoperability and software reuse. The third group is the gaming and Internet community. Their efforts are mostly focused on developing realistic scenarios in distributed environments.

Parallel and distributed simulation can provide four major advantages [Fuj99]:

1. Enabling execution of simulations that otherwise could not be performed. Executing a large system after subdividing it in simpler, smaller parts enables shorter execution times. This enables using real-time simulations to support timecritical decision-making processes in cases where a single computer cannot achieve the required performance. Moreover, distributed environments allow the execution of larger, more complex simulations whose memory requirements exceed the resources available in a single computer.

- 2. *Geographical distribution*. It is possible to distribute the execution at different physical locations, which is particularly interesting for some applications where data or users are not located in a central location.

- 3. *Integrating simulators based on different platforms*. Simulations can be carried out using different computers, operating systems, and simulators.

- 4. *Fault tolerance*. When using multiple processors, it becomes possible to increase the tolerance to failures in a simulation; if a node fails, a surviving node may take over and continue the execution.

**Synchronization** is key when executing applications in parallel and distributed environments. A **logical process** (**LP**) is a basic entity in a simulation. An LP receives and generates timestamped events or messages to communicate with other LPs, which might execute in a different processor or machine. The synchronization mechanism ensures that each LP complies the **local causality constraint**, which requires that events should be processed in their timestamp order.

There are two main classes of algorithms for synchronization. **Conservative algorithms** offer a pessimistic approach. They avoid violating causality constraints at all times during the execution of a simulation. **Optimistic algorithms** allow some violations to happen, but provide a mechanism to detect and recover from these situations. Optimistic algorithms have two main advantages over conservative approaches: (i) they enable greater degrees of parallelism, and (ii) they do not rely on application-specific data to determine events that are safe to process, which is usually the case in conservative approaches. A different way for improving simulation performance and reducing execution times deals with the structure of the simulator. **Hierarchical simulation** mechanisms incur in greater overheads due to an increased number of exchanged messages that travel up and down the entire structure. **Flat simulation** approaches have been implemented in distributed [Kim00a] and stand-alone [Gli02a, Gli02d] environments, aiming to reduce the overhead by simplifying the structure. It has been shown that flat simulation approaches outperform the hierarchical mechanisms in virtual-time and real-time simulators [Gli02b, Gli02c].

A hierarchical, conservative parallel simulation mechanism has been implemented in CD++ [Tro01a]. Results have shown that parallel simulations outperformed singleprocessor simulations for both DEVS and Cell-DEVS models in CD++ [Tro01b]. However, since it implements a pessimistic synchronization mechanism, the degree of parallelism and the corresponding speedups are bounded. Moreover, studies showing that hierarchical approaches worsen execution performance encourage the implementation of a flat distributed simulator.

### 1.1 CONTRIBUTION

This dissertation presents the design and implementation of a new technique for optimistic simulation of Parallel DEVS and Cell-DEVS models in distributed environments. Our simulation methodology is based on the Parallel DEVS abstract simulator [Cho94b] and the Time Warp synchronization mechanism [Jef85]. The Time Warp algorithm allows simulation objects to process events optimistically, assuming events sent from remote LPs will not cause rollbacks in the future. If a remote LP sends such a message, simulation objects have to rollback optimistically processed events and continue the normal execution of the model from that point.

We introduce two new classes of DEVS processors that carry out the simulation efficiently across multiple machines. The proposed simulation algorithms use a flat simulation approach that eliminates the need for intermediate coordinators. Consequently, it reduces the overhead of message passing, improving the overall performance of the simulation.

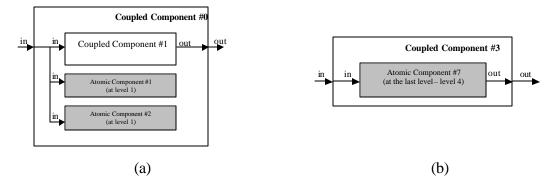

The new simulation technique is implemented in the CD++ toolkit, and its efficiency is measured using DEVS and Cell-DEVS models. Moreover, instead of restricting our efforts on testing individual models, we developed DEVStone, a synthetic benchmark to study the performance of DEVS-based simulators. Different factors were considered in order to create such synthetic models, which resemble real world applications. We focused on the main factors that have a significant impact on performance. Our benchmark supports generating models that have different structure, size and behavior. Two parameters define the general structure and size of a DEVStone model, namely depth and width. The depth of the model describes the number of levels in the overall structure. The width of the model specifies the number of components in each intermediate level. DEVStone supports three different types of models. Each model type is characterized by the number and complexity of interconnections between inner components. Finally, models execute different workloads that represent the real world processes to be performed by components of the application.

Using DEVStone, it is possible to assess the performance of a simulator using a large set of models with diverse characteristics. Since the structure and behavior of the models are known, it is also possible to compare the performance of different simulators. In order to obtain meaningful results, we use different types of models focusing on issues that can impact the execution performance. For example, we study the effect of executing models that are predominantly wide (i.e., a large number of models per level) or deep (i.e., a large number of levels in the modeling hierarchy). Using a heterogeneous test set, it is possible to analyze the performance of the simulators under different scenarios.

The accuracy and reliability of DEVStone relies on the automatic generation and execution of a large pool of diverse models, which provides a robust test set. This enables an analysis of performance with relation to the characteristics of a category of models of interest. The scope of this work is the execution of medium to large size models, defined as models composed of a minimum of 30 components. DEVStone can be used to assess the efficiency of DEVS simulation engines for these types of models, and it provides a common metric to compare the results using different tools.

We conduct a performance analysis using DEVStone to study the overhead of the new mechanism. A comparison between its performance and other engines provided by CD++ is provided. Although the overhead associated with synchronization tasks implemented by our simulator can be considerable, it presents good performance results when compared with more simple techniques. Based on these tests, we observed overheads for DEVS models is in the range of 2.5% to 5%. For Cell-DEVS models, we

present a performance analysis on distributed environments using models with different size and partition strategies showing significant execution speedups.

### **1.2 THESIS ORGANIZATION**

This work is organized as follows. Chapter 2 introduces the DEVS and Cell-DEVS formalisms, as well as some general concepts on parallel and distributed simulation with special focus on Time Warp synchronization. A survey on existing DEVS-based tools is presented. We also review the design of the CD++ simulator and provide some examples of DEVS and Cell-DEVS models. Chapter 3 discusses the simulation mechanisms provided by CD++ and other tools. Then, we introduce basic ideas about our new simulation technique. In Chapter 4, we present the design of our flat, optimistic simulator for DEVS and Cell-DEVS. We introduce the new algorithms that carry out distributed simulation, providing sample scenarios to better understand how they work. Chapter 5 discusses the implementation issues related to the distributed CD++ simulator. Chapter 6 introduces a synthetic benchmark for DEVS-based tools. A performance analysis of the new simulator that uses DEVStone and other models is presented. Finally, Chapter 7 provides our conclusions and future work.

# Chapter 2: DISCRETE EVENT MODELING AND SIMULATION TECHNIQUES

This chapter provides background information about the DEVS and Cell-DEVS formalisms and their extensions. The two main synchronization approaches for distributed simulation are also discussed, focusing on the optimistic alternative chosen for this work. We survey several M&S tools based on DEVS. Then we review the design of the CD++ simulator and some examples of models are given. Finally, this dhapter presents Warped and MPI, which are used to implement the optimistic CD++ simulator.

### 2.1 DEVS AND PARALLEL DEVS FORMALISMS

Systems whose variables are discrete and where time advance is continuous are known as DEDS (Discrete Event Dynamic Systems), as opposed to CVDS (Continuous Variable Dynamic Systems) which, in general, can be described by differential equations. Simulation mechanisms for DEDS systems assume that changes of state will take place upon the occurrence of an event. Formally, an event is defined as a change of state that occurs at a specific point of time  $t_i \in \mathbb{R}$ .

**DEVS** (Discrete Events systems Specification) [Zei76, Zei00], a formalism for modeling and simulating DEDS systems, defines a way to specify systems whose states change either upon the reception of an input event or due to the expiration of a time delay. It allows hierarchical decomposition of the model by defining a way to couple existing DEVS models. A real system modeled using DEVS can be described as a composition of *atomic* and *coupled* components. An *atomic* model is defined by:

$$M = \langle X, Y, S, \delta_{int}, \delta_{ext}, I, ta \rangle$$

where

$$\begin{split} X &= \{(p,v) | \ p \in \text{IPorts}, v \in X_p\} & \text{ is the set of input ports and values;} \\ Y &= \{(p,v) | \ p \in \text{OPorts}, v \in Y_p\} & \text{ is the set of output ports and values;} \\ S & \text{ is the set of sequential states;} \\ \delta_{ext} : Q \times X \to S & \text{ is the external state transition function;} \end{split}$$

where  $Q = \{ (s,e) / s \in S, e \in [0, ta(s)] \}$  and e is the elapsed time since the last state transition.

| $\delta_{\text{int}} : S \to S$     | is the internal state transition function; |

|-------------------------------------|--------------------------------------------|

| $\lambda{:}\:S\to Y$                | is the output function;                    |

| ta: $S \rightarrow R_0^+ U \propto$ | is the time advance function;              |

A DEVS model is in a state  $s \in S$  at any given time. In the absence of external events, it remains in that state for a lifetime defined by ta(s). A transition that occurs due to the consumption of time indicated by ta(s) is called an internal transition. When ta(s) time expires, the system outputs the value  $\lambda(s)$  and then changes to a new state given by  $\delta_{int}(s)$ . On the other hand, an external transition occurs due to the reception of an external event. In this case, the external transition function determines the new state, given by  $\delta_{ext}(s, e, x)$  where *s* is the current state, *e* is the time elapsed since the last transition and  $x \in X$  is the external event that has been received.

The time advance function can take any real value between 0 and  $\infty$ . A state for which ta(s) = 0 is called a transient state. In contrast, if the  $ta(s) = \Psi$  then s is said to be a passive state, in which the system will remain perpetually unless an external event is received.

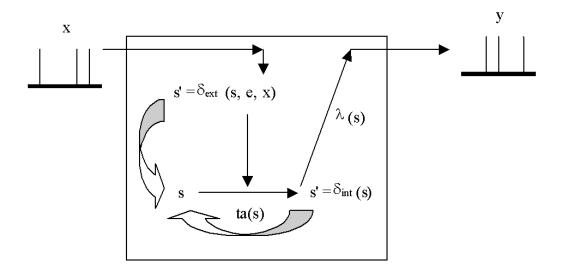

The following figure shows the description of states and variables in DEVS models:

Figure 2: DEVS semantics

A DEVS *coupled model* is composed of several atomic or coupled submodels. It is formally defined by:

$$CM = \langle X, Y, D, \{M_d | d I D\}, EIC, EOC, IC, select \rangle$$

where

$$X = \{(\mathbf{p}, \mathbf{v}) | \mathbf{p} \ \hat{\mathbf{I}} \ IPorts, \mathbf{v} \ \hat{\mathbf{I}} \ X_p\}$$

is the set of input ports and values;

$$Y = \{(\mathbf{p}, \mathbf{v}) | \mathbf{p} \ \hat{\mathbf{I}} \ OPorts, \mathbf{v} \ \hat{\mathbf{I}} \ Y_p\}$$

is the set of output ports and values;

*D* is the set of the component names, and the following constraints apply to the components, which are also DEVS models:

for each  $d \hat{I} D$

$M_d = (X_d, Y_d, S, \boldsymbol{d}_{ext}, \boldsymbol{d}_{int}, \boldsymbol{d}_{con}, \boldsymbol{l}, ta)$  is a DEVS basic structure,

where

$X_d = \{(\mathbf{p}, \mathbf{v}) | \mathbf{p} \ \hat{\mathbf{I}} \text{ IPorts}, \mathbf{v} \ \hat{\mathbf{I}} \ X_p \},\$

$Y_d = \{(\mathbf{p}, \mathbf{v}) | \mathbf{p} \ \hat{\mathbf{I}} \ OPorts, \mathbf{v} \ \hat{\mathbf{I}} \ Y_p\}$ , and the couplings are subject to the following conditions:

external input couplings (EIC) connect external inputs to component inputs, EIC  $\hat{\mathbf{I}}$  {((N,  $ip_N$ ), (d,  $ip_d$ )) /  $ip_N \hat{\mathbf{I}}$  IPorts, d  $\hat{\mathbf{I}}$  D,  $ip_d \hat{\mathbf{I}}$  IPorts<sub>d</sub>}

external output couplings (EOC) connect component outputs to external outputs, EOC  $\hat{I}$ {((d, op<sub>d</sub>), (N, op<sub>N</sub>)) / op<sub>N</sub>  $\hat{I}$  OPorts,  $d\hat{I}$  D, op<sub>d</sub>  $\hat{I}$  OPorts<sub>d</sub>}

$\left(\left(a, op_{a}\right), \left(1, op_{N}\right)\right) = op_{N} + of ons, a + b, op_{a} + of ons_{a}\right)$

*internal couplings (IC)* connect component outputs to component inputs, IC  $\mathbf{\hat{I}}$  {((a, op a), (b, ip\_b)) / a, b  $\mathbf{\hat{I}}$  D,  $op_a \mathbf{\hat{I}}$  OPorts<sub>a</sub>,  $ip_b \mathbf{\hat{I}}$  IPorts<sub>b</sub> }

Direct feedback loops are not allowed, i.e., no output port of a component may be connected to an input port of the same component. Formally,

$((d, op_d), (e, ip_d)) \in IC$  implies  $d^{-1} e$ .

The values sent from a source port must be within the range of accepted values of a destination port (range inclusion constraint). Formally,

$\forall ((N, ip_N), (d, ip_d)) \ \hat{I} \ EIC : X_{ipN} \ \hat{I} \ X_{ipd}$

$\forall ((a, op_a), (N, op_N)) \ \hat{I} \ EOC : Y_{opa} \ \hat{I} \ Y_{opN}$

$\forall$  ((a,  $op_a$ ), (b,  $ip_b$ ))  $\hat{I}$  IC :  $Y_{opa}$   $\hat{I}$   $X_{ipb}$ .

*select* is the tie-breaker function, where *select*: subset of  $D \rightarrow D$ , such that for any non-empty subset E, *select* (E)  $\in$  E.

A coupled model groups several DEVS into a compound model that can be regarded, due to the *closure property*, as a new DEVS model. The closure property guarantees that the coupling of several class instances results in a system of the same class [Zei00]. This property allows hierarchical model construction.

In addition, each coupled model has its own input and output events, as defined by the X and Y sets. When external events are received, the coupled model has to redirect the inputs to one or more components. Similarly, when a component produces an output, it may have to map it as an input to another component, or as an output of the coupled model itself. Mapping between ports is defined by the Z function.

Multiple components can be scheduled for an internal transition at the same time in a coupled component, and ambiguity may arise. If the first component to execute its internal transition produces an output that maps to an external event for another component that is already scheduled for an internal transition, then it is not clear which transition this second component should execute first. Two alternatives exist: to execute the external transition first with e = ta(s) and then the internal transition, or else to execute the internal transition first followed by the external transition with e = 0. By the *select* function, the DEVS formalism enables a simple way to solve this ambiguity. The function defines an order over the components so that only one component of the group of imminent models is allowed to have e = 0. The other imminent models are divided in two groups: those that receive an external output from this model, and the rest. The former will execute their external transition functions with e = ta(s), the latter will be imminent during the next simulation cycle which may require again the use of the *select* function to decide which model will execute first. This strategy for tiebreaking is rigid and, in addition, it introduces serialization in the execution of components. The serialization introduced by this approach becomes visible when the *select* function has to be used to determine the priority in which the components have to be executed. For example, the *select* function is used to determine which atomic component has priority over the rest to execute its internal transition function when many interconnected atomic models are imminent.

**Parallel DEVS** or **P-DEVS** [Cho94a] is an extension to DEVS that provides a more flexible way of dealing with these ambiguities. Atomic models provide an additional confluent function to specify collision behavior for events that might be scheduled simultaneously. Since serialization constraints existing in the original DEVS formalism are now eliminated, P-DEVS permits increased degrees of parallelism that can be exploited in parallel and distributed environments. Consequently, Parallel DEVS was the formalism chosen as the foundation for this work.

P-DEVS models are described very much like DEVS models. An atomic Parallel DEVS model is defined as:

$$\mathbf{M} = \langle X_M, Y_M, S, \boldsymbol{d}_{ext}, \boldsymbol{d}_{int}, \boldsymbol{d}_{con}, \boldsymbol{l}, ta \rangle$$

where

| $X_M = \{(p,v)   p \in \text{ IPorts, } v \in \mathbb{C}\}$   | $X_p$            | is the set of input ports and values;  |

|---------------------------------------------------------------|------------------|----------------------------------------|

| $Y_M = \{(p,v)  \ p \in \ OPorts, \ v \in$                    | $Y_p$ }          | is the set of output ports and values; |

| S                                                             | is the set of se | quential states;                       |

| $\delta_{ext}: Q \ge X_M^{\ b} {\rightarrow} S$               | is the external  | state transition function;             |

| $\delta_{\text{int}}:S\to~S$                                  | is the internal  | state transition function;             |

| $\delta_{\text{con}} : Q \mathrel{x} X_M{}^b {\rightarrow} S$ | is the confluer  | nt transition function;                |

| $\lambda:S\to {Y_M}^b$                                        | is the output f  | unction;                               |

| $ta:S\to {R_{\scriptscriptstyle 0}}^+\cup\infty$              | is the time adv  | vance function;                        |

|                                                               |                  |                                        |

with  $Q = \{(s, e) \mid s \in S , 0 \le e \le ta(s)\}$  the set of total states.

There are two main differences between a basic DEVS and a basic Parallel DEVS model. First, the external transition function uses a bag of events instead of a single event. This allows multiple events to be processed simultaneously. Since external events received by the component are added to a bag,  $X_M^b$ , external transition functions can combine the functionality of a number of external transitions into a single one. Second, the model specification includes a confluent transition function  $(\delta_{con})$ . When a collision between the internal and external functions occurs, the confluent function determines the new state of the model.

The semantics of P-DEVS are similar to those of DEVS. A basic model is in a state *s* at any given time. In the absence of external events, the model remains in that state for a lifetime period defined by ta(s). When that time expires, an internal transition takes place; the system outputs the value I(s) and then it changes to the state specified by

$d_{inf}(s)$ . If one or more external events  $E = \{x_1 \dots x_n / x \in X_M\}$  occurs before ta(s) expires, i.e., while the system is in total state (s, e) with e < ta(s), the new state will be given by the model's external transition function,  $d_{ext}(s,e,E)$ . P-DEVS allows a better way to deal with collisions. External and internal transitions are in conflict when external events E are received when e = ta(s). In such cases, the new state of the model can be given by  $d_{ext}(d_{int}(s),e,E)$  or  $d_{int}(d_{ext}(s,e,E))$ . Hence, modelers have a flexible way of indicating the appropriate behavior for each model in the confluent function  $(d_{con})$ , which is triggered in case of collisions.

In P-DEVS, coupled models are defined as in DEVS without the need for a *select* function. Formally, a coupled model is defined as:

$$CM = \langle X, Y, D, \{M_d \mid d \ \hat{I} \ D\}, EIC, EOC, IC \rangle$$

The definitions for the set of input and output events (X and Y), components (D and  $M_d$ ), and couplings (*EIC*, *EOC*, and *IC*) follow the specifications of DEVS coupled models presented earlier in this chapter.

If multiple components in a coupled model are imminent, all their outputs are first collected and mapped to their influencees. Then, the corresponding transition function is executed for every model.

### 2.2 MODELING CELL SPACES

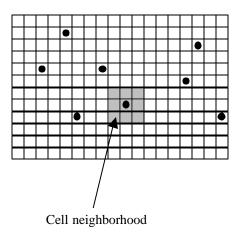

Different formalisms have been used to capture the behavior of systems that can be represented as cell spaces. Examples of such systems can be found in many fields, from chemistry to engineering, from physics to social sciences. Cellular Automata [Wol86] is a well-known formalism that describes this type of systems. A cellular automaton is an infinite regular *n*-dimensional lattice whose cells can take one finite value. States in the lattice are updated according to a local rule in a simultaneous, synchronous way. The cell states change in discrete time steps using a local transition function that considers the current state of the cell and a finite set of nearby cells (called the neighborhood of the cell).

Figure 3: Sketch of a cellular automaton [Wai00]

### 2.2.1 The Timed Cell-DEVS formalism

The Timed Cell-DEVS formalism [Wai98] uses the DEVS paradigm to define a cell space where each cell is defined as a DEVS atomic model. As a result, it is possible to build discrete event cell spaces improving their definition by making the timing specification more expressive. A Cell-DEVS atomic model is defined in [Wai98] as:

TDC = < X, Y, I, S, ? , N, d,  $\delta_{int}, \delta_{ext}, t$  , ? , D >

where

*X* is a set of external input events;

*Y* is a set of external output events;

*I* represents the model's modular interface;

*S* is the set of sequential states for the cell;

*T* is the cell state definition;

*N* is the set of states for the input events;

*d* is the delay for the cell;

$\delta_{int}$  is the internal transition function;

$\delta_{ext}$  is the external transition function;

*t* is the local computation function;

? is the output function; and

D is the state duration function.

A cell uses a set of input values N to compute its future state, which is obtained by applying the local computation function t. A delay function is associated with each cell, deferring the output of the new state to the neighbor cells. This activation of the local computation is carried by the  $\delta_{ext}$  function.

After the basic behavior for a cell is defined, a complete cell space can be constructed by building a coupled Cell-DEVS model:

$GCC = < X_{list}, \, Y_{list}, \, I, \, X, \, Y, \, n, \, \{t_1, ..., t_n\}, \, N, \, C, \, B, \, Z, \, \textit{select} > 1$

where

$X_{list}$  is the input coupling list;

$Y_{list}$  is the output coupling list;

*I* represents the definition of the interface for the modular model;

*X* is the set of external input events;

*Y* is the set of external output events;

*n* is the dimension of the cell space;

$\{t_1,...,t_n\}$  is the number of cells in each of the dimensions;

*N* is the neighborhood set;

*C* is the cell space;

*B* is the set of border cells;

*Z* is the translation function; and

select is the tie-breaking function for simultaneous events.

This specification defines a coupled model composed of an array of atomic cells. Each cell is connected to the cells defined in its neighborhood. Nevertheless, as the cell space is finite, either the borders are provided with a different neighborhood than the rest of the space, or they are *wrapped* (cells in one border are connected with those in the opposite one). Finally, the *Z* function defines the internal and external coupling of cells in the model. This function translates the outputs of m-th output port in cell  $C_{ij}$  into values for the m-th input port of cell  $C_{kl}$ . Each output port will correspond to one neighbor and each input port will be associated with one cell in the inverse neighborhood. The *select* function serves the same purpose as in the original DEVS models: to tiebreak among imminent components.

The use of the *select* function in Cell-DEVS introduces similar problems to those introduced by DEVS, namely lack of parallelism exploitation and possible inconsistency

with the real system. In addition, the timed Cell-DEVS has another restriction: only one input can arrive from each input port. Such restriction disallows zero-delay transitions and external DEVS models sending two simultaneous events to the same cell [Wai00]. Forbidding zero-delay transitions and the limitation of only one event per external model is very restrictive, and led to an extension of the formalism.

**Parallel Cell-DEVS** is a revision of the Cell-DEVS formalism that eliminates such restrictions [Wai00]. The author shows two important properties: i) Parallel Cell-DEVS models are equivalent to parallel DEVS models, and ii) closure under coupling for parallel Cell-DEVS models also holds, i.e., a coupled parallel Cell-DEVS model is equivalent to a basic parallel Cell-DEVS model. An implementation of Parallel Cell-DEVS was presented in [Tro03].

### 2.3 DEVS-BASED TOOLKITS FOR M&S

Several tools have been implemented based on DEVS theory and its extensions, reflecting the level of interest from the community. Some of the existing DEVS M&S toolkits are listed next.

- ADEVS [Nut04] provides a C++ library based on DEVS, which developers can use to build their own models, and supports integration with other simulation environments.

- DEVS-C++ [Zei96] is a DEVS-based modeling and simulation environment written in C++, which implements parallel execution and supports large-scale systems.

- DEVS-Scheme [Zei93] is a knowledge-based environment for modeling and simulation based on the DEVS formalism, supporting real-time simulation.

- DEVS/Grid [Seo04], a JAVA-based simulator for Grid computing infrastructures, was developed focusing on performance and scalability. It supports cost-based model partitioning, remote simulator activation, and dynamic coupling restructuring.

- DEVS/HLA [Zei99a] is based on the High Level Architecture (HLA) [HLA00]. It was used to demonstrate how an HLA-compliant DEVS environment could improve the performance of large-scale distributed modeling and simulation.

- DEVSCluster [Kim00b, Kim04] is a multi-threaded, CORBA-based simulator for DEVS models that supports simulation in heterogeneous network environments.

- DEVSJAVA [Sar98] is a DEVS-based modeling and simulation environment written in Java. It provides classes for the users to implement their own DEVS models.

- DEVSim++ [Kim94] is an object-oriented software to simulate DEVS models, which was implemented in C++. The tool defines basic classes that can be extended by users to define their own atomic and coupled DEVS components.

- GALATEA [Dav00b] is a simulation platform that offers a language to model multiagent systems using an object-oriented architecture. The tool describes a real system as a set of interacting agents.

- JAMES [Him04] implements DEVS theory to model and simulate agent systems. The toolkit supports software-in-the-loop simulation to test agents in virtual environments.

- JDEVS [Fil02a] is a DEVS modeling and simulation environment written in Java. It allows general purpose, component-based, object-oriented, visual simulation of models.

- PyDEVS uses the ATOM3 tool [Del02] to construct DEVS models and to create the code to be executed. Models are represented as a state graph used to generate Python code and then interpreted by PyDEVS.

- SimBeams [Pra99] is a component-based software architecture based on Java and JavaBeans. The idea is to provide a set of layered components that can be used in model creation, result output analysis and visualization using DEVS.

The majority of the existing toolkits support stand-alone simulation. Some of them, such as DEVS-C++, DEVS/HLA, DEVSCluster, D-DEVSim++ [Kim96] (an extension to DEVSim++), and DEVSJAVA allow distributed execution of DEVS models. The middleware technology that enables parallel and distributed simulation varies from tool to tool. Some of these technologies are:

- CORBA (Common Object Request Broker Architecture) [OMG02], an open standard promulgated by the Object Management Group (OMG),

- HLA (High Level Architecture) [HLA00], a standard specifically designed for distributed simulations, and

- MPI [Don96], a message passing interface standard designed for high performance communication on parallel and distributed environments.

Some of the approaches exploit the specific parallelism existing in DEVS by implementing a pessimistic approach. In such cases, a unique global scheduler is in charge of synchronizing all nodes; only events with identical timestamp can be processed. As a result, the global scheduler often becomes a bottleneck that prevents achieving higher degrees of parallelism and speedups in a simulation [Kim96]. On the other hand, optimistic approaches give nodes more freedom to process events. In such cases, causality errors can occur but a mechanism to detect and recover from them has to be incorporated. Some efforts in optimistic simulation of DEVS models are summarized next.

DEVS-Ada/Tw [Chr90] was the first attempt to combine DEVS and Time Warp over a multiprocessor environment. However, the implementation imposes two important constraints. First, all models mapped in the same processor are treated as an indivisible logical process. In case of a rollback, the associated cost can be considerable because all the information of the LP has to be restored. Second, models can be divided only at the top level of the hierarchy, imposing a major restriction on users when determining partition boundaries. The second constraint makes the approach inflexible in terms of partition strategies, as it is not possible to divide a model at lower levels of its hierarchy. For example, a system composed by two coupled models can only be partitioned in two processors (one machine running each coupled model), regardless of the internal structure of its coupled models.

The Distributed Optimistic Hierarchical Simulation (DOHS) scheme combines DEVS and Time Warp, implemented in D-DEVSim++ [Kim96]. This alternative presents a more general approach for distributed optimistic execution of DEVS models, while addressing the two major restrictions introduced by DEVS-Ada/TW: DOHS rollback mechanism allows simulation objects to be rolled back individually, and it supports model partition at any level of the hierarchy.

DEVSCluster [Kim00b, Kim04] is an object-oriented, multi-threaded, distributed simulator that implements a combination of Time Warp and DEVS simulation based on the ideas presented in [Kim96]. However, instead of using the classic message passing approach, DEVSCluster uses CORBA-based method invocation for advancing the simulation. In [Kim04], the authors present a non-hierarchical approach for more efficient distributed simulation.

A risk-free optimistic synchronization mechanism is proposed in [Zei97b], focused on applications that interact with geographically distributed real-world components. In this approach, only safe outputs are sent (avoiding propagation of rollbacks to remote processors so that rollbacks can always be kept local). This mechanism is well suited for shared memory multiprocessor platforms, but has limitations in distributed heterogeneous architectures.

DEVS/P2P [Che04] is an implementation of a distributed DEVS simulator over a layered peer-to-peer network system. The proposed algorithm does not require a coordinator for scheduling purposes; simulators solve synchronization issues by themselves following a decentralized mechanism. Nodes use peer discovery functions to find the location of remote resources.

#### 2.4 THE CD++ TOOLKIT

CD++ [Rod99, Wai02, Tro03] is a M&S toolkit that implements the original and Parallel DEVS and Cell-DEVS formalisms. The tool was built as a hierarchy of classes in C++, where each class corresponds to a simulation entity using the basic concepts defined in [Zei76, Zei00].

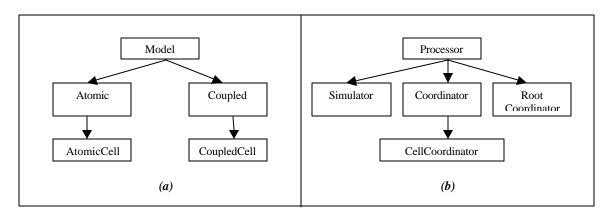

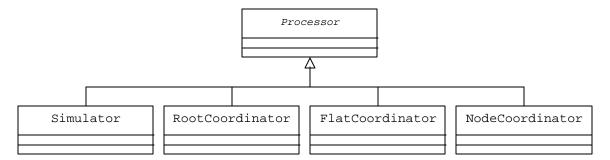

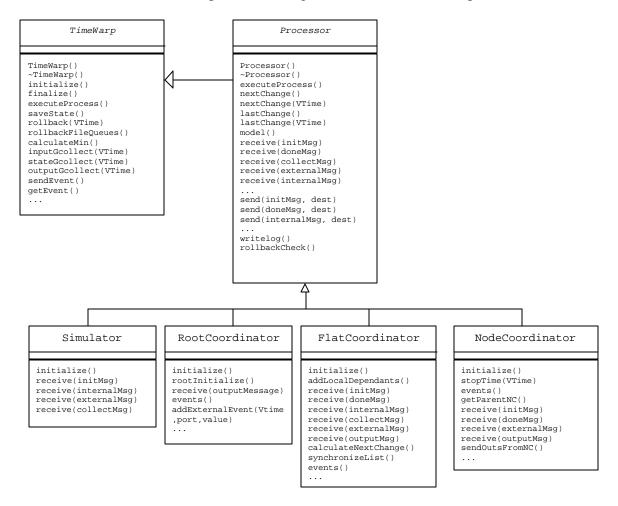

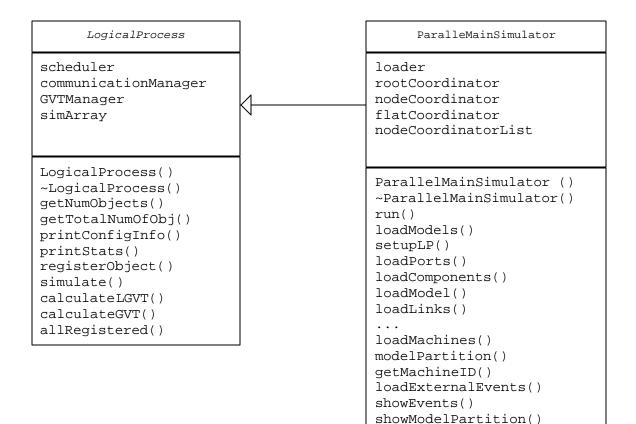

There are two basic abstract classes: *Model* and *Processor*. The former is used to represent the behavior of the atomic and coupled models, while the latter implements the simulation mechanisms. Figure 4 shows the CD++ class hierarchy.

Figure 4: CD++ (a) Model hierarchy, (b) Processor hierarchy

The *Atomic* class implements the behavior of an atomic component. The *Coupled* class implements the mechanisms of a coupled model. For cellular models, special atomic models are used to represent the cells. To do so, *AtomicCell* and *CoupledCell* are defined as subclasses of *Atomic* and *Coupled* respectively. *AtomicCell class* extends the behavior of the atomic models, to define the functionality of the cell space. In contrast, *CoupledCell* handles a group of atomic cells.

A *simulator* object manages an associated atomic object, handling the execution of its  $\delta_{int}$ ,  $\delta_{ext}$ ,  $\delta_{con}$  and  $\lambda(s)$  functions. A *coordinator* object manages an associated coupled object. Only one *root coordinator* exists in a simulation. It manages global aspects of the simulation. It is involved with the topmost-coupled component, which has the highest level in the model hierarchy. Moreover, the *root coordinator* maintains the global time, and it starts and stops the simulation process. Lastly, it receives the output results that must be sent to the environment.

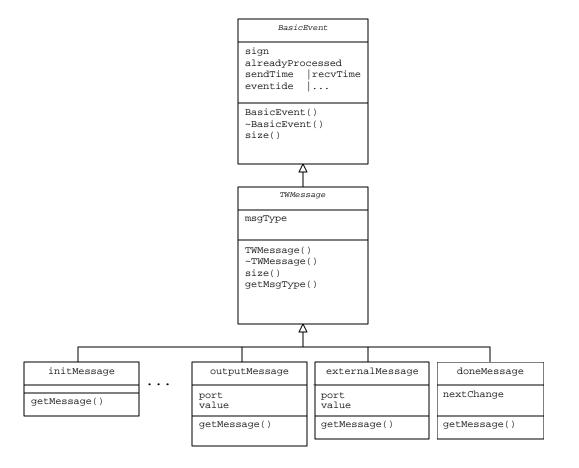

The simulation process is message driven; processors exchange messages to advance the execution of the model. Each message contains information to identify the *sender* and the *receiver*. A *time-stamp* for the message and an associated *value* are also included in the packet. Two main categories of messages exist: synchronization and content messages. These categories consist of several types of messages.

#### Synchronization messages:

- *@ Collect message*

- \* Internal message

- done *Done message*

# **Content messages:**

- q External message

- y *Output message*

### *Processors* have internal variables to keep the time of the simulation:

t<sub>L</sub> Time of last transition

#### t<sub>N</sub> Time of next transition

and a *bag* to store external messages.

The tool provides a specification language that allows describing coupling of models, initial values and external input events. Atomic models are developed under C++, which provides a great flexibility and computing power to the modeler. Each new atomic model must inherit from the *Atomic* class in order to extend their basic behavior.

New atomic models are written in C++ and have to be derived from the class *Atomic*. The methods that determine the behavior of an atomic model are:

- *initFunction*, which is executed when the simulation starts, and usually initializes the model variables,

- o externalFunction, which is executed when an external event is received,

- *internalFunction*, which is executed when an internal transition is scheduled, and

- *outputFunction*, which generates the output of the model and is executed before the internal transition function.

CD++ provides functions that can be used from the atomic models, including:

- *holdIn(state, time)*. It is used to specify that the model must remain in a state for the specified time.

- *passivate()*. When this function is called, the model enters in passive mode

(i.e., ta = ∞), and only external events can change its state.

- *sendOutput(p, v)*. This function sends an output message with a value of v through the output port p.

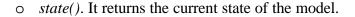

Figure 5: Diagram of atomic model Controller Unit

Figure 5 shows the scheme of an atomic model. This is a controller unit used in an automated manufacturing system (AMS) built with CD++ [Gli04]. An AMS is formed by dedicated stations that perform tasks on products being assembled, and conveyors that

transport the products to/from those workstations. The controller is connected to other components: sensors, a scheduler, conveyor belts, and a digital display. Input ports (e.g., station\_1A and sensor\_2A, which are connected with the scheduler) and output ports (e.g., station\_display\_A, which is connected to the digital display, and direction\_A, which is connected with the engine of the conveyor belt) allow the controller unit to communicate with those components.

Figure 6 and Figure 7 show the specification of the controller unit in CD++. The constructor of the class, *ControllerUnit::ControllerUnit*, creates the input and output ports of the model. The initialization function, *initFunction*, initializes some of the controller's variables (e.g., current station, next required station, activation of sensors, direction of the conveyor belt) for both production lines (A and B). The external transition function specifies the behavior of the controller unit upon the reception of events from the sensors and the scheduler. For example, upon the activation of a sensor, the conveyor belt A has to be stopped when the requested station is reached. The method *holdIn()* is called to trigger an internal transition function after the time indicated as a parameter (in this case, since the specified time is zero, then the internal function is executed immediately).

```

ControllerUnit::ControllerUnit

( const string &name ) : Atomic( name ),

station_1A( addInputPort( "station_1A" ) ),

station_2A( addInputPort( "station_2A" ) ),

station_3A( addInputPort( "station_3A" ) ),

. . .

sensor_3B( addInputPort( "sensor_3B" ) ),

sensor_4B( addInputPort( "sensor_4B" ) ),

station_display_A( addOutputPort( "station_display_A" ) ),

. . .

direction_display_B( addOutputPort( "direction_display_B" ) ),

{ }

Model &ControllerUnit::initFunction()

ł

req_station_A = 1;

curr_station_A = 1;

sensors_enabled_A = 1;

direction_A = 0;

. . .

req_station_B = 1;

curr_station_B = 1;

sensors_enabled_B = 1;

. . .

}

Model &ControllerUnit::externalFunction

( const ExternalMessage &msg )

{

if (sensors_enabled_A)

if( msg.port() == sensor_1A )

{

if (req_station_A == 1)

{

stop_engine_A = 1;

. . .

holdIn( active, VTime::Zero );

}

if( msg.port() == sensor_2A )

if( msg.port() == sensor_3A )

. . .

. . .

}

```

Figure 6: Specification of atomic model Controller Unit in CD++ (part 1)

Figure 7 contains the internal and output functions for the controller unit. The output function is executed before the internal transition function. Following the same example, when the engine of the conveyor belt A has to be stopped, a value of 0 is sent via the port *activate\_A* using the method *sendOutput*. The internal transition function enables and disables the sensors depending on the values of the current and requested stations for each production line and it passivates the model (i.e., sets the next internal transition time to infinity).

```

Model &ControllerUnit::internalFunction

const InternalMessage &msg )

(

if ( !sensors_enabled_A && (req_station_A==cur_station_A) )

ł

sensors enabled A = 1;

passivate();

return *this ;

}

Model &ControllerUnit::outputFunction

( const InternalMessage &msg )

{

if (stop_engine_A == 1)

sendOutput( msg.time(), activate_A, 0) ;

if (stop_engine_B == 1)

sendOutput( msg.time(), activate_B, 0) ;

```

Figure 7: Specification of atomic model Controller Unit in CD++ (part 2)

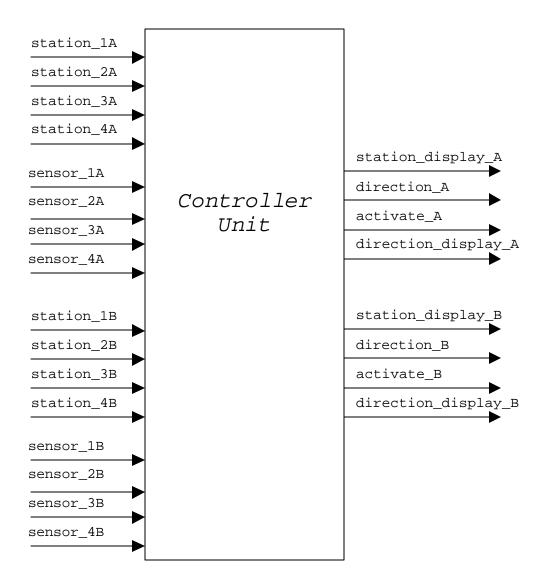

CD++ allows users to combine multiple basic models (i.e., atomic or coupled) into a coupled model using a specification language that follows DEVS definitions. Using this specification language, it is possible to define external input couplings, external output couplings and internal couplings, and components that form the model. Let us continue with the previous example of the automated factory. The entire AMS, formed by a scheduler, a controller unit, a display controller, and two conveyor belts, can be seen as a new coupled model. This coupled model is composed of atomic (e.g., controller unit) and coupled components (e.g., conveyor belt), as outlined in Figure 8.

Figure 8: Diagram of the coupled model AMS

Figure 9 shows the specification of the AMS coupled model in CD++.

```

components: conveyor_A

conveyor_B

scheduler@Scheduler

components

cu@CU

dis@Display

: start_A start_B

in

out : status_conveyor_A

out : status_conveyor_B

link : start A start A@scheduler

link : start B start B@scheduler

. . .

link : sensor 1@conveyor A

sensor 1@cu

link : sensor 2@conveyor A sensor 2@cu

. . .

link : dir display A@cu dir display A@dis

link : status conv A@cu status conv A@dis

link : dir display B@cu dir display B@dis

link : status_conv_B@cu status_conv_B@dis

. . .

[conveyor_A]

components: sb@SensorController

eng@Engine

in : activate direction

out : sensor_1 sensor_2 sensor_3 sensor_4

link : activate

activate@eng

link : direction direction@eng

link : sensor_1@sb sensor_1

. . .

link : current_pos@eng sensor_triggered@sb

. . .

[conveyor B]

components: sb@SensorController

eng@Engine

. . .

```

Figure 9: Specification of coupled model AMS in CD++

The components for the top model follow the architecture shown in Figure 8. Here, *conveyor\_A* and *conveyor\_B* are coupled components, whereas *cu*, *scheduler*, and *dis* are atomic. The top model input ports, *start\_A* and *start\_B*, are used to trigger the production cycle for lines A and B. The output ports, *status\_conveyor\_A* and *status\_conveyor\_B*, provide information about the state of products in each line. The keyword *link* defines connections between components. For example, the *start\_A* in the top model port is connected to the *start\_A* port in the *scheduler*, and the *sensor\_1* port of *conveyor\_belt\_A* is connected to the port *sensor\_1* of the controller unit (*cu*). Cell-DEVS models are also defined using a built-in specification language. Users specify different parameters of the system such as size of the model, cell neighborhood, type of borders (wrapped or non-wrapped), type of delay (transport or inertial), and the rules that determine the behavior of each cell. Figure 10 shows the specification for the popular "life" game [Gar70] as a Cell-DEVS model in CD++ [Wai02].

```

[top]

components : life

[life]

type : cell

width : 20

height : 20

delay : transport

defaultDelavTime : 100

border : wrapped

neighbors : life(-1,-1) life(-1,0) life(-1,1)

localtransition : conrad-rule

neighborports : value

[conrad-rule]

rule : { ~value := 1; } 100 { (0,0)~value = 1

and (statecount(1, ~value) = 3)

or statecount(1, ~value) = 4) }

rule : { ~value := 0; } 100 { (0,0)~value = 1

and (statecount(1, ~value) < 3)

or statecount(1, ~value) > 4) }

rule : { ~value := 1; } 100 { (0,0)~value = 0 and statecount(1, ~value) = 3 }

rule : { ~value := 0; } 100 { (0,0)~value = 0 and statecount(1, ~value) != 3 }

```

Figure 10: Specification of Cell-DEVS model life in CD++

This life model is defined as a 20x20 wrapped Cell-DEVS model with transport delays and 3x3 neighborhood. The behavior of each cell is defined by the rules of the model. Rules have the form of *VALUE DELAY {CONDITION}*; when the *CONDITION* is satisfied, the cell state becomes *VALUE* and then it is *DELAY* for the specified time. In this case, the survival of a cell that is active (or alive) depends on the number of active cells within its neighborhood. If the number of active cells, determined by

statecount(1, ~value), is three or four the cell remains alive (specified by the first rule), otherwise it dies (specified by the second rule). The third rule specifies that an inactive cell becomes active if the number of active cells in its neighborhood is three. In this model, the delay is 100 milliseconds for every rule.

CD++ provides several operations, such as Boolean (AND, OR, NOT, IMP, and EQV), comparison (=, !=, <, >, <=, and >=), and arithmetic, as well as numerous functions, such as trigonometric, rounding, truncation, logarithmic, minimum, and maximum.

Nowadays, CD++ is the only simulation tool that implements Parallel Cell-DEVS, although there are numerous tools that support the execution of cellular automata, for example MJCell [Woj04], Cellsprings [Ell04], Trend [Cho02], SpaSim [Mor02], and JCASim [Fre01]. Some of these tools support parallel execution to reduce simulation time. CD++ enables visualization of Cell-DEVS in 2D and 3D using different shapes and colors to better understand the results of a simulation [Wai03].

The algorithms for simulator, coordinator, and root coordinator implemented in CD++ can be found in [Tro03], and are based on those presented in [Cho94b].

#### 2.5 PARALLEL AND DISTRIBUTED SIMULATION

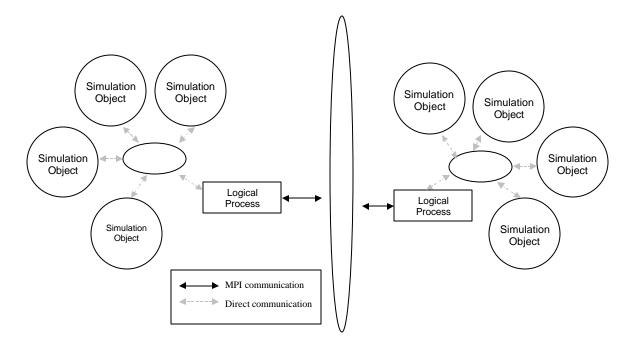

**Parallel discrete event simulation** (PDES) is focused on the execution of discrete event simulations in distributed environments. In parallel and distributed simulations, the execution of a system is subdivided in smaller, simpler parts that run on different processors or nodes. Each of these subparts is a sequential simulation, which is

usually referred to as a logical process (LP). A logical process groups one or more simulation objects running in a node.

Simulator objects communicate with each other exchanging timestamped messages or events to advance the simulation. Objects located on different LPs have to traverse the boundaries of the LPs to interact with each other in an activity known as inter-LP communication. Those running on the same LP can also interact with each other, in this case without crossing the boundaries of any LP, by means of intra-LP communication.

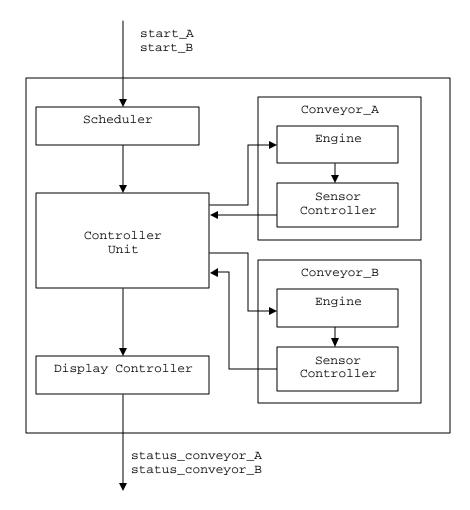

For example, let us consider the distributed simulation of a system described earlier: an automated manufacturing system formed by workstations, conveyor belts, and loading and storing subsystems. Products move through the factory using the conveyor belts. Items have to be loaded, workstations must perform actions (e.g., polishing, varnishing, cutting, painting) on them and, lastly, completed items are stored. The simulation of such a system is distributed across two logical processes, as outlined in Figure 11: one to control the workstations and conveyor belts (LP<sub>1</sub>) and the other for the loading and storing subsystems (LP<sub>2</sub>).

When an item is loaded and ready to be processed, the loading system (running on  $LP_2$ ) places it on the corresponding conveyor belt (running on  $LP_1$ ). This event requires inter-LP communication (shown in Figure 11 with a dashed line from *Conveyor Belt* to *Workstation B*); a message has to be sent from  $LP_2$  to  $LP_1$ . In contrast, interactions among workstations and conveyor belts require only intra-LP communication (shown in Figure 11 with a solid line). Simulation objects that interact frequently should be placed in the

same LP, since intra-LP communication usually requires less time than inter-LP communication. In contrast, simulation objects that seldom interact should be placed in different machines to take advantage of parallelism [Rao98].

Figure 11: Automated Manufacturing System partitioned in two LPs

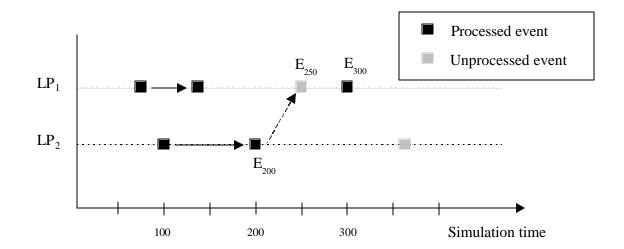

Let us extend our example. If one wants to reduce the execution times, it may seem reasonable to concurrently execute events received on different LPs in order to exploit parallelism. A possible scenario of two LPs processing events is shown in Figure 12. Consider two events:  $E_{200}$  with timestamp 200 received in LP<sub>2</sub> node and  $E_{300}$  with timestamp 300 received in LP<sub>1</sub>. Suppose that there are no unprocessed events before 200 (in LP<sub>2</sub>) and before 300 (in LP<sub>1</sub>). In this situation, it might seem reasonable to process  $E_{200}$  and  $E_{300}$ . Now, suppose that the execution of  $E_{200}$  in LP<sub>2</sub> generates a new event  $E_{250}$  with timestamp 250, which is sent to LP<sub>1</sub> (shown in Figure 12 with a dashed line from LP<sub>2</sub> to LP<sub>1</sub>). When LP<sub>1</sub> receives the event  $E_{250}$ , it was already processing the event  $E_{300}$  with timestamp 300. Although it was received later, the event  $E_{250}$  happens before  $E_{300}$  and therefore should have been processed first. For example,  $E_{250}$  may represent a signal that requires immediate attention and affects the results of processing  $E_{300}$ .

Figure 12: Violation of local causality constraint in a distributed simulation The local causality constraint [Fuj99] addresses this type of situations:

*Local causality constraint.* A discrete-event simulation formed by logical processes that interact by exchanging timestamped messages obeys the local causality constraint if and only if each LP processes events and messages in nondecreasing timestamp order.

This brings us to a fundamental issue in parallel and distributed simulations known as synchronization. Simulations in distributed environments rely on synchronization algorithms that either avoid or deal with local causality constraints. The goal of a synchronization algorithm is to ensure that the distributed simulation of the system yields the same results as the sequential case.

Notice that the synchronization mechanism does not need to guarantee that all events are always processed in their timestamp order, but the final results must coincide with the results obtained by sequential simulation [Fuj99].

There are two major classes of synchronization strategies: conservative and optimistic. Next, we briefly describe each of them with more focus on the latter, which is used in this work.

#### 2.5.1 CONSERVATIVE SIMULATION

Conservative approaches, also known as pessimistic approaches, were the first synchronization algorithms proposed for distributed simulations. The general idea behind them is that no local causality errors shall ever happen upon processing an event. In other words, an event is processed in a node if it can be guaranteed that no other event with smaller timestamp will be received in the future. Therefore, a situation like the one illustrated in Figure 12 can never happen.

The Chandy-Misra-Bryant (CMB) algorithm [Bry77, Cha79, Mis86] is a wellknown conservative algorithm developed in the late 1970s. Since the requirement introduced by conservative algorithms introduces deadlocks, the original CMB algorithm was extended with *null* messages (which are exchanged among LPs) to deal with this situation. Null messages indicate a lower bound of the subsequent messages that will be sent by an LP, and allow advancing the simulation, while breaking the deadlock. A wellknown problem of the CMB algorithm is that larger numbers of null messages may lead to poor simulation performance: the communication overheads can become considerable high.

Other conservative algorithms based on CMB detect and recover from deadlocks [Cha81] instead of avoiding them. A different algorithm, proposed by Chandy and Sherman, relies on more detailed event-related information and can achieve better performance in many cases [Cha89]. Unfortunately, newer algorithms require more application specific data to exploit greater degrees of parallelism.

Although many conservative algorithms are currently found in real-world applications, they have two main disadvantages [Fuj90]:

- It is not possible to take advantage of the concurrency available in the application, since they have to adhere to the local causality constraint at all times.

- ii) The simulation program has to be specifically designed to exploit concurrency, leading to a complex, tedious design process. In relation to this, small changes in the application may worsen the performance of the simulation in a great way, since changes may affect data used for efficient conservative simulation.

#### 2.5.2 OPTIMISTIC SIMULATION

Instead of avoiding violations to the local causality constraint, like conservative algorithms do, optimistic algorithms allow some causality errors to occur but provide means to recover from them, which in the end leads to correct results.

Optimistic approaches address the two fundamental disadvantages of conservative algorithms:

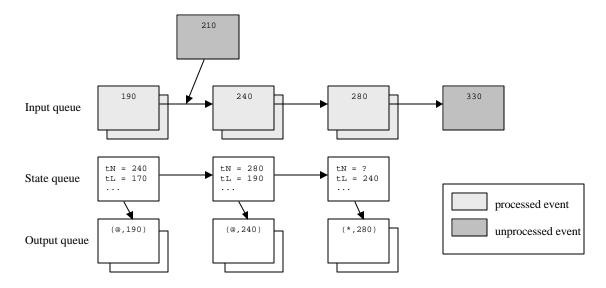

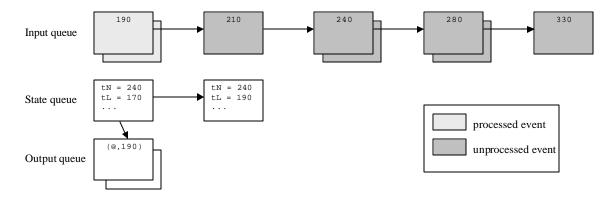

- They can exploit higher degrees of concurrency by advancing the simulation optimistically. These approaches assume that causality errors will not arise. If a causality error occurs, the optimistic algorithm has to detect and recover from that situation.