## E-CD++: AN ENGINE FOR EXECUTING DEVS MODELS IN EMBEDDED ENVIRONMENTS

By

**Yinfeng Henry Yu**

## A thesis submitted to The Faculty of Graduate Studies and Research

In partial fulfilment for the degree of Master of Applied Science in Systems and Computer Engineering

Ottawa-Carleton Institute for Electrical and Computer Engineering Department of Systems and Computer Engineering Carleton University Ottawa, Ontario Canada © Copyright 2007, Yinfeng Henry Yu

## ACKNOWLEGEMENTS

I would like to thank the invaluable supervision and support from Dr. Gabriel Wainer during the development of this work. Working with him has been a challenging and yet rewarding experience.

I would also like to thank Carleton University, especially the department of Systems and Computer Engineering, for providing the excellent research opportunities and facilities.

This thesis is dedicated to my wife, Rui. Without her enduring support and prayers, this work may not be able to complete.

## Abstract

The DEVS (Discrete Event System Specification) formalism defines a formal Modelling and Simulation (M&S) framework for Discrete Event Dynamic Systems (DEDS). The RT-DEVS formalism is a real-time extension to DEVS. RT-DEVS is adequate to model Real-time Embedded Systems (RTES). This work introduces the Embedded CD++ (E-CD++) toolkit. It provides an execution engine that can run DEVS models in embedded environments. E-CD++ supports the RT-DEVS formalism, and can be used as a development tool for RTES. The target system can be first studied and modelled entirely in DEVS. The DEVS models are then executed by E-CD++ on embedded platforms where they can interact with the real-world events in real time. In E-CD++ execution environment, the DEVS models can also interact with real hardware surrogates. When a DEVS component is fully tested in the embedded environment, it can be replaced by its physical counterpart, and this step can be repeated until all the components are replaced by their target counterparts. This development approach enables instantaneous transition from modelling to implementation. We also made more efforts than just implementing RT-DEVS in order to make E-CD++ an adequate real-time execution engine. We improved E-CD++ performance by deploying the Flattened Coordinator Technique. We also implemented the GGAD Graphical Modelling tool, so that the modeller can define DEVS models using graphical notations. Lastly, to illustrate with real applications, we used E-CD++ to built an Automated Manufacturing System (AMS), which is a real-time application consisting of microprocessors and mechanical devices.

## **Table of Contents**

| CHAPTER | R 1 INTRODUCTION                         | 1   |

|---------|------------------------------------------|-----|

| 1.1     | CONTRIBUTIONS                            |     |

| 1.2     | THESIS ORGANIZATION                      |     |

| СНАРТЕБ | R 2 M&S FOR EMBEDDED SYSTEMS DESIGN      | 9   |

| 2.1     | M&S METHODOLOGIES                        | 9   |

| 2.2     | THE ORIGINAL DEVS FORMALISM              |     |

| 2.3     | PARALLEL DEVS FORMALISM                  |     |

| 2.4     | REAL-TIME DEVS (RT-DEVS) FORMALISM       |     |

| 2.5     | APPLYING DEVS TO EMBEDDED SYSTEMS DESIGN |     |

| 2.6     | DEVS-BASED SIMULATION TOOLKITS           |     |

| 2.7     | M&S METHODS FOR RTES DESIGN              | 25  |

| СНАРТЕВ | R 3 EMBEDDED CD++ (E-CD++)               | 27  |

| 3.1     | CD++                                     | 27  |

| 3.2     | E-CD++                                   |     |

| 3.3     | GGAD GRAPHICAL NOTATION                  | 29  |

| 3.4     | P-DEVS SIMULATION ALGORITHMS             |     |

| 3.5     | FLATTENED COORDINATOR TECHNIQUE          | 42  |

| 3.6     | TIME INTERVAL FUNCTION                   | 45  |

| СНАРТЕВ | R 4 E-CD++ SOFTWARE ARCHITECTURE         | 50  |

| 4.1     | E-CD++ SOFTWARE ARCHITECTURE OVERVIEW    | 50  |

| 4.2     | MAIN SIMULATOR                           |     |

| 4.3     | MODELLING SUBSYSTEM                      | 57  |

| 4.4     | GGAD MODEL LOADER                        | 61  |

| 4.4.1   | GGAD Parser                              | 63  |

| 4.4.2   | 2 GGAD Symbol Table                      | 65  |

| 4.4.3   | 3 GGAD Syntax Tree                       | 68  |

| 4.4.4   | 4 GGAD Transitions Execution Engine      | 74  |

| 4.4.5   | 5 GGAD Atomic Model Adaptor              | 77  |

| 4.5     | SIMULATION SUBSYSTEM                     | 79  |

| 4.6     | MESSAGING SUBSYSTEM                      |     |

| СНАРТЕВ | R 5 CASE STUDY                           | 86  |

| 5.1     | MODELLING THE AMS                        | 86  |

| 5.1.1   | l Hybrid System Modelling                | 90  |

| 5.1.2   |                                          |     |

| 5.2     | MODEL EXECUTION USING E-CD++             |     |

|         | Executions of Simulated Components       |     |

| 5.2.2   |                                          |     |

| 5.2.3   |                                          |     |

| СНАРТЕВ | R 6 CONCLUSIONS                          | 109 |

| 6.1     | FUTURE WORK                              | 110 |

| СНАРТЕВ | R 7 REFERENCES                           | 111 |

| APPENDI | IX A E-CD++ SYSTEM ARCHITECTURE          | 114 |

| A.1.   | THE CLIENT-SERVER SYSTEM ARCHITECTURE | 114 |

|--------|---------------------------------------|-----|

| A.2.   | THE SBC BOOTING SEQUENCE              | 115 |

| APPEND | DIX B GRAMMAR FOR GGAD MODELS         |     |

|        | CONTEXT-FREE GRAMMAR FOR GGAD MODELS  |     |

| B.2.   | Tokens:                               | 119 |

|        | GGAD BUILT-IN FUNCTIONS               |     |

# List of Figures

| Figure 1          | The basic entities and their relationships [Zei00]                                       | 10 |

|-------------------|------------------------------------------------------------------------------------------|----|

| Figure 2          | DEVS Semantics [Gli04]10                                                                 |    |

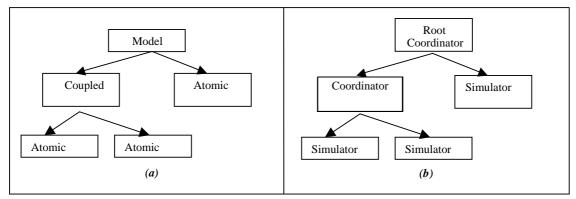

| Figure 3          | CD++ (a) Model hierarchy, (b) Processor hierarchy                                        | 28 |

| Figure 4          | Graphical definition of an atomic model: Coin Displayer                                  | 30 |

| Figure 5          | GGAD textual definition of the coin model                                                | 31 |

| Figure 6          | Simulator Receiving Collect Message                                                      | 36 |

| Figure 7          | Simulator Receiving External Message                                                     | 36 |

| Figure 8          | Simulator Receiving Internal Message                                                     | 37 |

| Figure 9          | Coordinator Receiving Collect Message                                                    | 38 |

| Figure 10         | Coordinator Receiving Output Message                                                     | 39 |

| Figure 11         | Coordinator Receiving External Message                                                   | 39 |

| Figure 12         | Coordinator Receiving Internal Message                                                   | 40 |

| Figure 13         | Root Coordinator Behaviours                                                              | 41 |

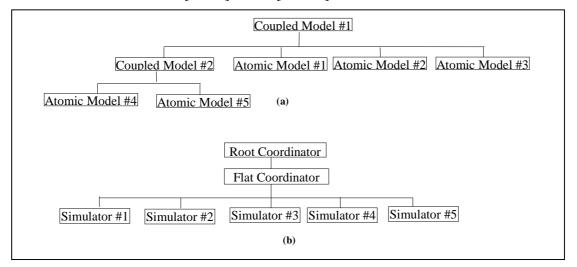

| Figure 14         | CD++ (a) Model hierarchy, (b) Processor hierarchy [Gli04]                                | 42 |

| Figure 15<br>proc | Flattened Coordinator Technique (a) Example of a model hierarchy, (b) Assessor hierarchy |    |

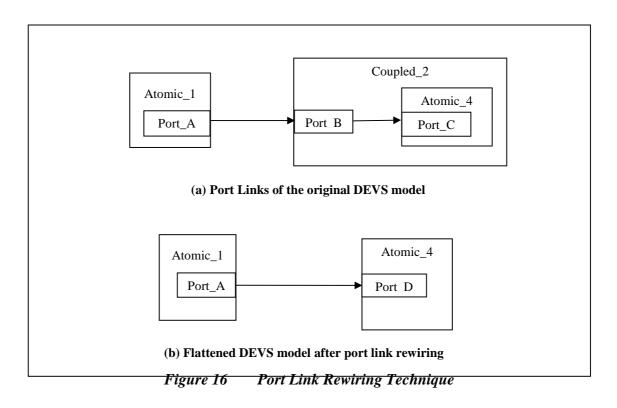

| Figure 16         | Port Link Rewiring Technique                                                             | 44 |

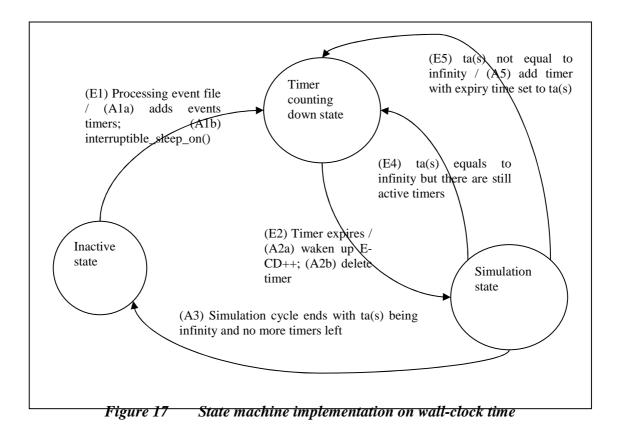

| Figure 17         | State machine implementation on wall-clock time                                          | 47 |

| Figure 18         | Format of the event file in the real time extension                                      | 48 |

| Figure 19         | Deadline checking algorithm                                                              | 49 |

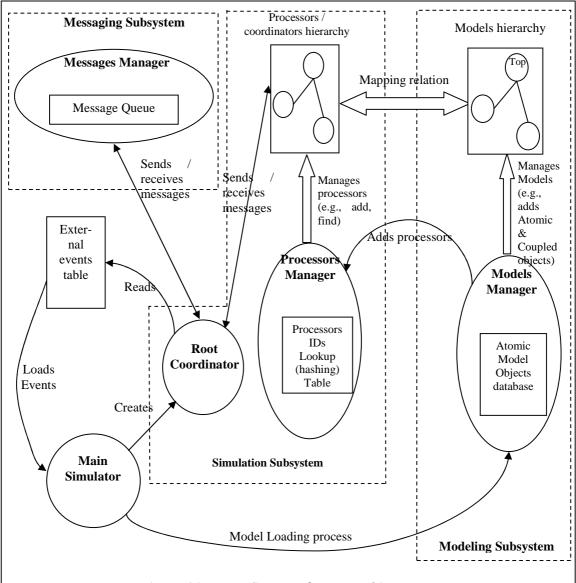

| Figure 20         | E-CD++ software architecture                                                             | 51 |

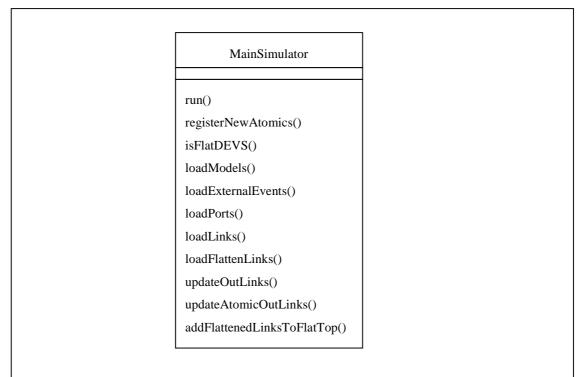

| Figure 21         | Main Simulator Class Diagram                                                             | 54 |

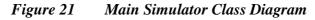

| Figure 22         | Port Link Rewiring by Flattened Coordinator Technique                                    | 57 |

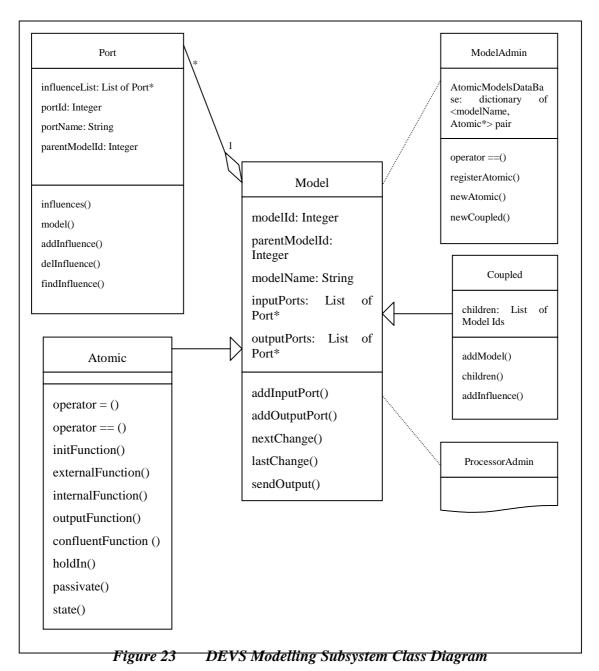

| Figure 23         | DEVS Modelling Subsystem Class Diagram                                                   | 58 |

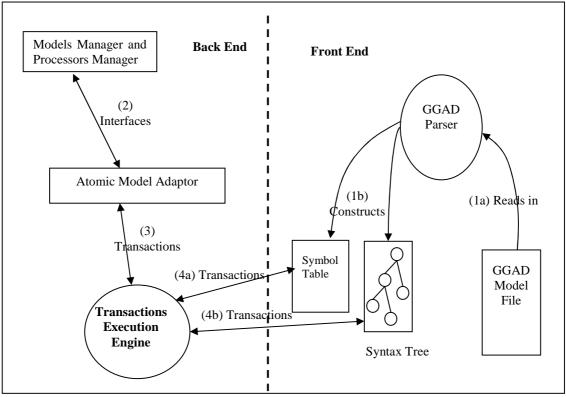

| Figure 24         | GGAD Model Loader Architectural Overview                                                 | 62 |

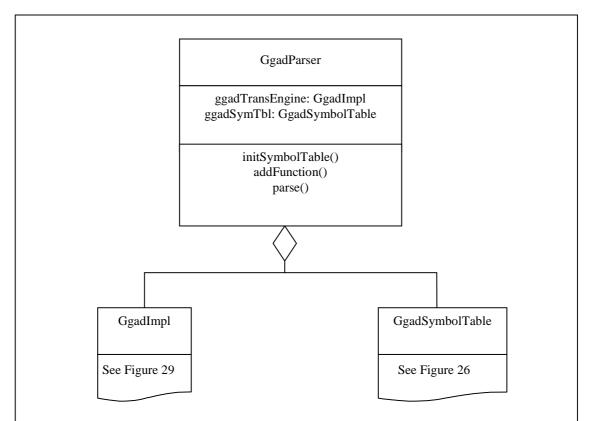

| Figure 25         | GGAD Parser Class Diagram                                                                | 64 |

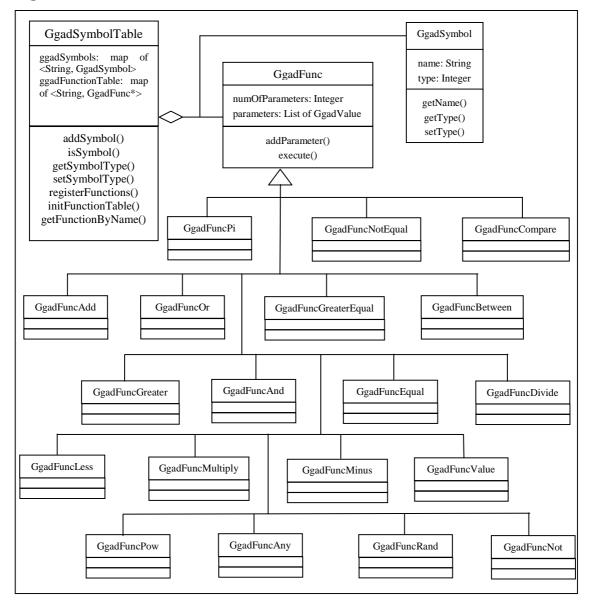

| Figure 26         | GGAD Symbol Table Class Diagram                                                          | 66 |

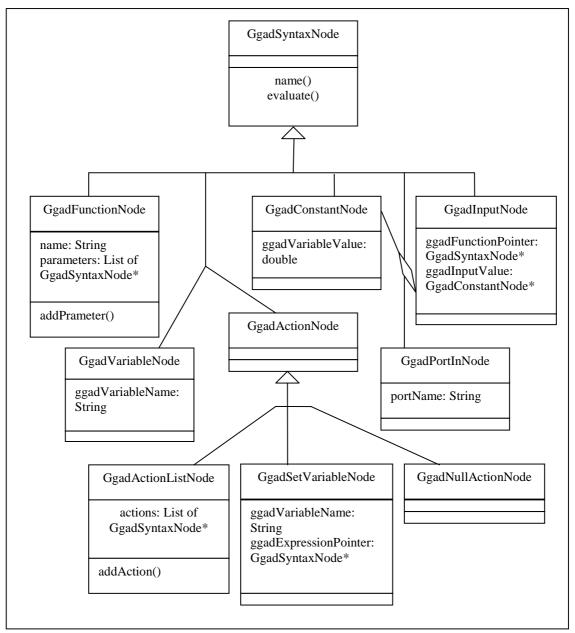

| Figure 27         | GGAD Syntax Tree Class Diagram                                                           | 70 |

| Figure 28         | Context grammar of GGAD internal and external transition functions                       | 72 |

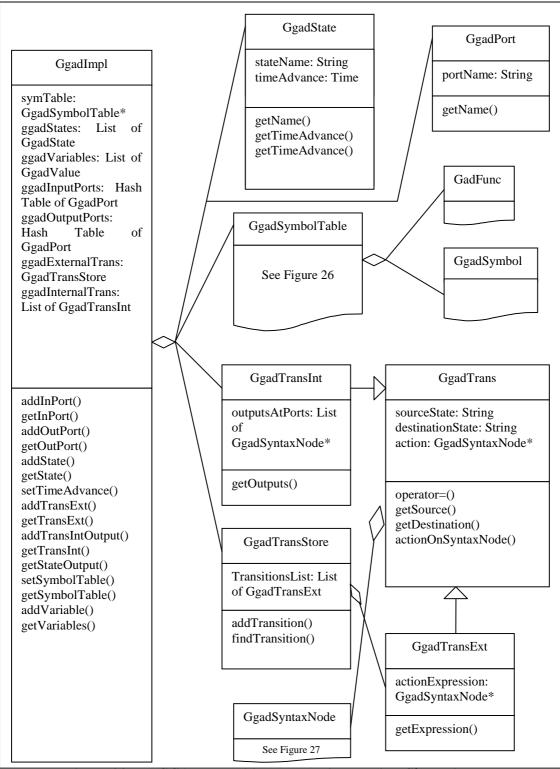

| Figure 29         | GGAD Transitions Execution Engine Class Diagram                                          | 75 |

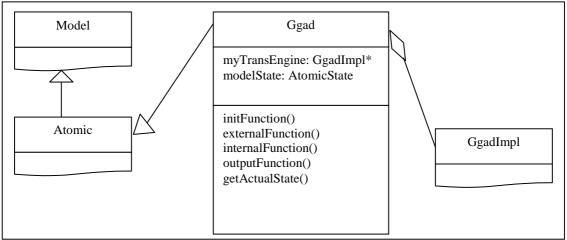

| Figure 30         | GGAD Atomic Model Adaptor Class Diagram                                                  | 78 |

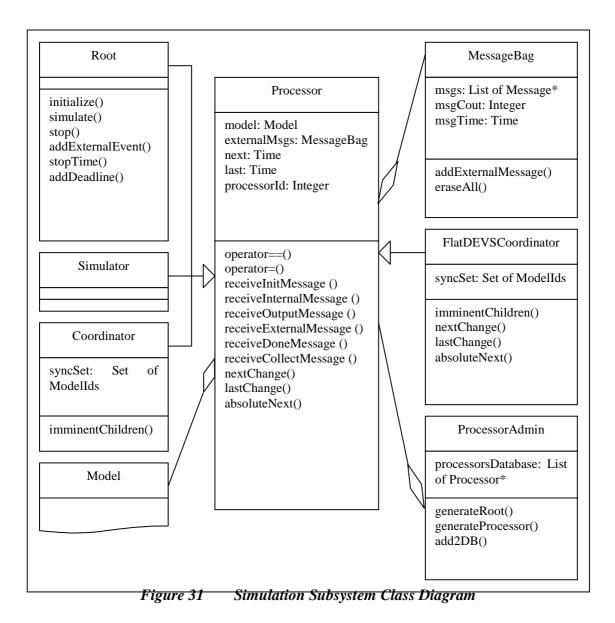

| Figure 31         | Simulation Subsystem Class Diagram                                                       | 80 |

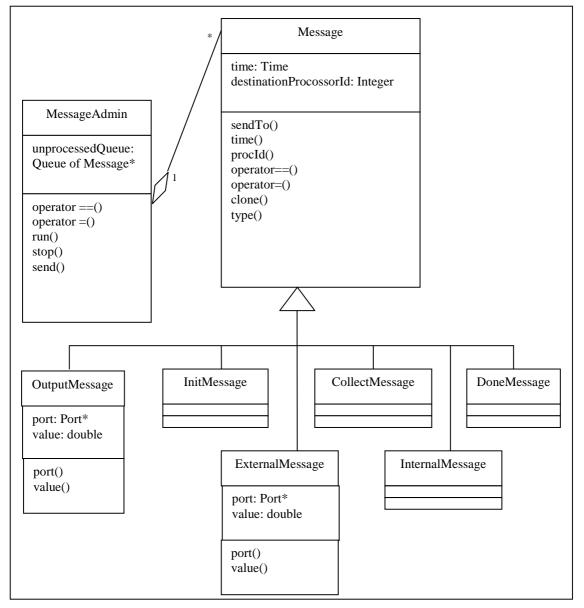

| Figure 32         | Messaging Subsystem Class Diagram                                                        | 83 |

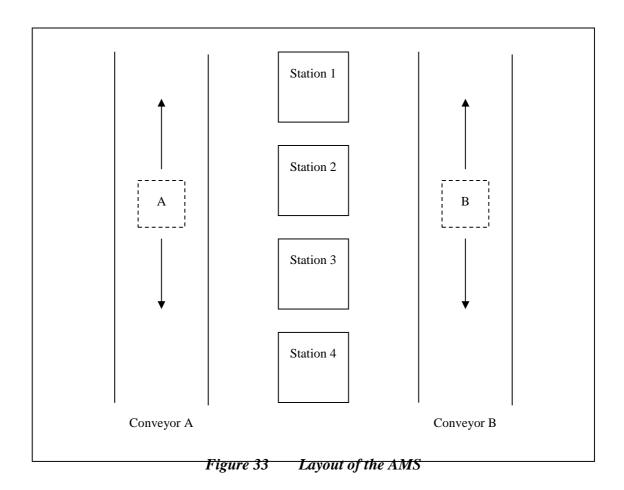

| Figure 33 | Layout of the AMS                                            | 87  |

|-----------|--------------------------------------------------------------|-----|

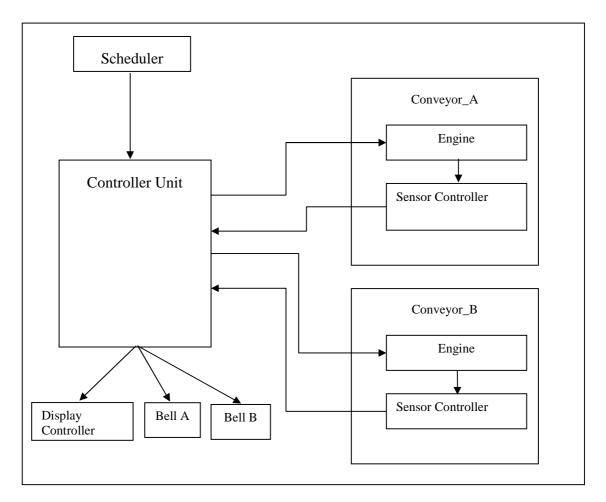

| Figure 34 | Scheme of the AMS                                            | 88  |

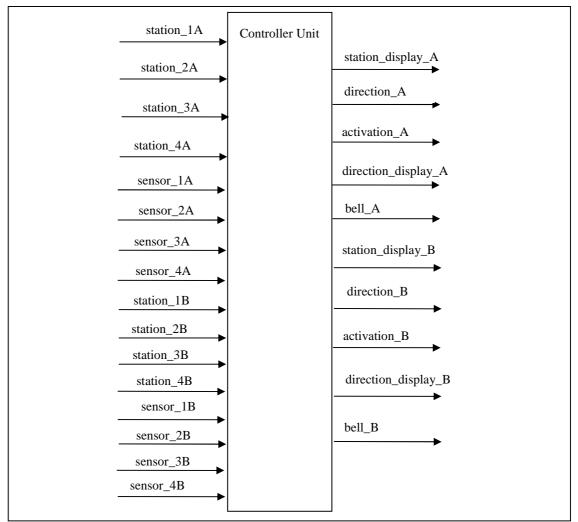

| Figure 35 | Diagram of the Controller Unit                               | 89  |

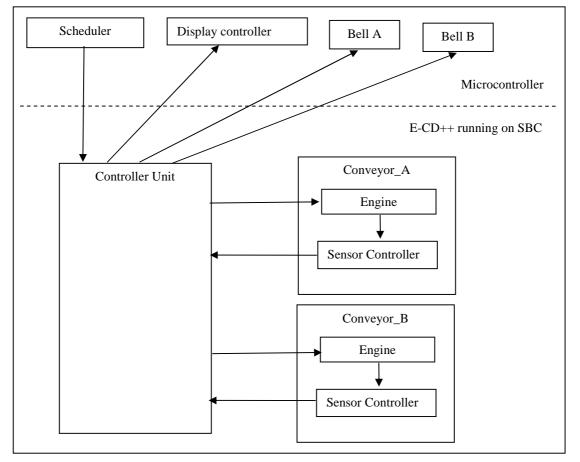

| Figure 36 | Hybrid AMS Scheme (scheduler, display and bells in hardware) | 91  |

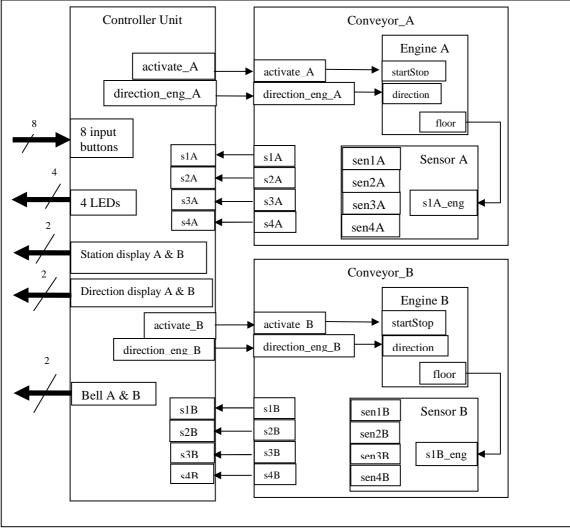

| Figure 37 | Definition of the AMS system in E-CD++                       | 93  |

| Figure 38 | Modelling Scheme of the Simulated Part of AMS                | 94  |

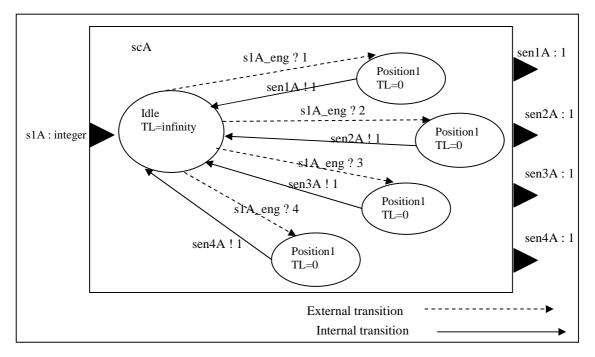

| Figure 39 | GGAD Graphical Notation of the Sensor Controller             | 95  |

| Figure 40 | GGAD Model File of the Sensor Controller                     | 95  |

| Figure 41 | The Sensor Class                                             | 97  |

| Figure 42 | An experimental event file generated by the scheduler        | 97  |

| Figure 43 | Simulation results displayed by the Display Controller       | 98  |

| Figure 44 | External Transition Function of the Engine Model             | 99  |

| Figure 45 | Internal Transition Function of the Engine Model             | 100 |

| Figure 46 | Output Function of the Engine Model                          | 101 |

| Figure 47 | Sample Message Log Trace                                     | 102 |

| Figure 48 | Message Log Generated During the AMS Simulation              | 104 |

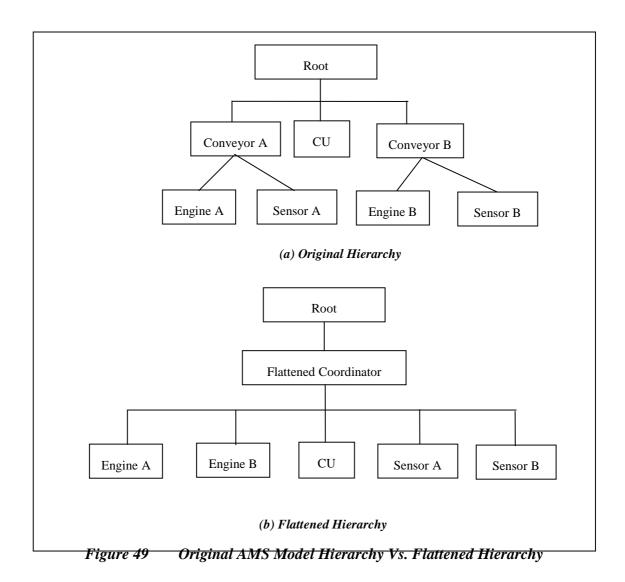

| Figure 49 | Original AMS Model Hierarchy Vs. Flattened Hierarchy         | 105 |

| Figure 50 | Confluent Function of the Controller Unit                    | 107 |

| Figure 51 | A schedule events file that can cause conflicts              | 107 |

| Figure 52 | Output results generated by non-parallel CD++                | 107 |

| Figure 53 | Output results generated by parallel CD++                    | 108 |

| Figure 54 | E-CD++ Software Architecture                                 | 114 |

## List of Tables

| Table 1         | GGAD Keywords                                                                                                     | 64 |

|-----------------|-------------------------------------------------------------------------------------------------------------------|----|

| Table 2<br>my_  | GGAD Built-in Functions (note: parameters a, b, c, d and e have double data type;<br>var and my_port are strings) | 67 |

| Table 3         | Behaviours of the evaluate() method in GGAD syntax node classes                                                   | 73 |

| Table 4         | Implementations of the Ggad class methods                                                                         | 78 |

| Table 5         | Various Types of Messages Supported by the Messaging Subsystem                                                    | 84 |

| Table 6         | The Hybrid AMS Model                                                                                              | 90 |

| Table 7<br>Tecl | Theoretical Vs. Experimental Performance Improvement Ratio of Flattened Coordin mique                             |    |

# List of Acronyms

| ASIC           | Application Specific Integrated Circuits        |

|----------------|-------------------------------------------------|

| AM             | Atomic Model                                    |

| AMS            | Automated Manufacturing System                  |

| API            | Application Programming Interface               |

| СМ             | Coupled Model                                   |

| CVDS           | Continuous Variable Dynamic Systems             |

| DEDS           | Discrete Event Dynamic Systems                  |

| DEVS           | Discrete Event System Specification             |

| E-CD++         | Embedded CD++                                   |

| FIFO           | First In First Out                              |

| FPGA           | Field Programmable Gate Array                   |

| FSM            | Finite State Machine                            |

| GGAD           | Generic Graphical Advanced environment for DEVS |

| GUI            | Graphical User Interface                        |

| M&S            | Modelling and Simulation                        |

| MSDE           | Modelling and Simulation-Driven Engineering     |

| P-DEVS         | Parallel DEVS                                   |

| <b>RT-DEVS</b> | Real-time DEVS                                  |

| RTES           | Real-time Embedded System                       |

| RTS            | Real-time System                                |

| SBC            | Single Board Computer                           |

| UML            | Universal Modelling Language                    |

| UML-RT         | UML for Real-Time                               |

### Chapter 1 Introduction

**Real-time systems (RTS)** can be characterized as those whose correctness of operation depends not only upon the logical correctness but also upon the time at which it is performed. Current state-of-the-art RTS are typically **embedded systems**, which are advanced computer applications consisting of hardware, software, and various mechanical and electrical devices. Examples are like nuclear power stations, Automated Manufacturing Systems and car airbags. These **Real-Time Embedded Systems (RTES)** typically deliver data from/to devices interacting with the surrounding environment within deadlines ranging at millisecond scales.

Due to unique characteristics of RTES, the RTES design needs to face several special challenges that need not to be dealt with by that of other systems:

- The design needs to meet the timeliness requirements. RTES must provide correct outputs to external events or inputs within a time limit. A RTES can be categorized as either a soft or a hard real-time system, depending on the strictness of its timeliness requirements. For hard real-time, the design must meet the timeliness requirements with zero tolerance on delay, while, for soft real-time, limited tolerance can be allowed for very small delays.

- The design needs to meet the constraints on resources requirements (e.g., limited memory and processing power). Many RTES may also have constraints on power consumption, because they are deployed in environments where grid-electricity is not commonly available (e.g., inside mobile phones or remote devices).

- The design needs to deal with the hardware/software partition problem. The embedded system design space is formed by combinations of hardware and software components, which is also referred to as *hardware/software codesign*. The design decision on dividing the target system into hardware and software

components is referred to as *hardware/software partitioning*. The hardware/software partition problem is NP-complete [KS03], which is why an optimal design for a RTES can be very hard to achieve.

- The design needs to cope with the target systems' increasing scalability requirements. With the advance of the manufacturing technologies, more and more hardware components (e.g., ASICs and FPGAs) are integrated to form a single RTES. Furthermore, RTES are making use of networking technologies to exchange information or inter-work among each other. Networking makes it possible for hundreds of devices working together to complete larger tasks. Consequently, scalability becomes an important design issue.

- The design needs to cope with the target systems' increasing complexity. With the rapid deployment of cheaper and more power microprocessors, RTES are capable of supporting more and more complex applications.

We find that, due to the challenges listed above, no adequate and robust design framework exists today that is capable of carrying out optimal design solutions to RTES. Our study show that the deficiencies of the existing development methods of RTES mainly come from two weak areas: the development lifecycle and the system verification. The deficiencies in the development cycle could be attributed to the fact that no unified methodology or design framework exists today that can be adequately applied throughout the entire design cycle. Some tools/methods are better in one development stage, while others are better in other stages. Consequently, different tools and methods are used in different development stages, resulting in inconsistencies among analysis, design, test, and implementation. Consequently, when the development tasks switch towards the target environment, the early models are often abandoned [WG02]. For example, in the analysis stage, MATLAB may be used to build mathematical models to analyze data and algorithms. However, these mathematical models are rarely used at the design stage, where UML (Unified Modelling Language) is a more commonly used tool. However, for the implementation phase, UML models are inadequate comparing with programming

languages, such as C, because UML models cannot be directly executed on the target systems with real-time performance.

Another area of deficiencies is system verification. Since the current state-of-the-art RTES are complex systems that consist of a mix of software embedded in and interacting with hardware components and that also need to respond to real-world events in real time, correctness of RTES design is very difficult to achieve. Although formal methods for RTES design are promising, they have difficulties in scaling up when the complexity of the system increases. **Modelling and Simulation (M&S)** techniques, instead, are adequate for testing particular conditions, regardless of the application's size. However, no M&S technique exists today that can provide the same degree of adequacy to study RTES as that provided by mathematical methods to study continuous variable systems. The lack of adequate formal modelling methods makes RTES development become an ad-hoc process that is expensive, time consuming and error prone. For example, current methods for software construction for RTES require a difficult and expensive testing effort with no guarantee for a bug-free product. [LG05] listed three current approaches to RTES testing, with none of them being adequate:

- Formal specifications. When applying formal specifications, the requirements of the System of Interest are formally defined, and formal methods are subsequently applied to prove correctness. These techniques have had some success, but they are difficult to apply when the complexity of the system scales up.

- M&S techniques. M&S techniques and tools are proved to be to be helpful in designing complex systems. Nevertheless, no practical or automatable approach exists to perform the transition that exists between the modelling and the development phases, and this often results in model artefacts being abandoned, resulting in increased initial costs. Consequently, even though they provide improved products, M&S studies are not carried out, or they are used for analyzing individual subsystems, later discarding the developed software.

Simultaneously, M&S frameworks are not as robust as their formal counterparts are.

• A third kind of technique widely used to ensure that a RTS conforms to a specification is Software Testing, i.e., the execution of the software system with actual values. Although this method cannot guarantee the correctness of the application, it provides a practical solution that tries covering the largest possible number of system use scenarios.

To overcome these problems, the solution is to develop a formal methodology that is adequate to be applied to every design stage throughout the entire development lifecycle. Modelling and Simulation-based Development of RTES relies on simulation based modelling for developments of RTES. We propose a novel Simulation-based Development framework for RTES, based on a formal method called DEVS (Discrete Event Systems specification) [Zei76, Zei00]. To be used as the final target architecture for products, DEVS provides a formal foundation to M&S that has been proven to be successful in different complex systems. We choose DEVS to model RTES because of the following reasons:

- The DEVS formalism is a formal method based on mathematical theories. So, the correctness of DEVS models can be formally validated.

- DEVS has well-defined concepts for coupling of components and hierarchical, modular model composition, which makes it adequate to model RTES.

- DEVS not only proposes a framework for model construction, but also defines an abstract simulation mechanism that is independent of the model itself. This mechanism provides a high level description of how the simulation of DEVS models should be executed. Based on this mechanism, it is possible to develop a real-time embedded execution environment in which DEVS models are run and

interact with the real hardware surrogates, so that the target system can be developed in hardware-in-the-loop.

Our methodology is based on successive prototyping and refinement, which combines the advantages of a simulation-based approach with the rigor of a formal methodology, which is well suited for RTES development. It consists of the following steps: Modelling phase, model verification phase, and Incremental Model replacement phase.

- 1. *Modelling phase*: The modeler defines the DEVS model for the target system. The modeler may have a choice to define the DEVS models using a high-level graphical notation, which makes it easier to understand system structure and behaviors.

- 2. *Model Verification phase*: This phase is concerned with the transformation of the model specification into an executable model. The models obtained from the previous phase are used to automatically derive simulation, and experimentation is done in a virtual environment. The simulation runs on high processing power workstations.

- 3. *Incremental Model Replacement phase*: Once the models are verified in a virtual environment, they are then executed in a real-time environment. The tested components are incrementally replaced by their target counterparts interacting with the actual setting.

- 4. This cycle is incrementally repeated up to the moment where the system is fully developed and tested.

This new methodology defines a unified design process for RTES. By simulating the models, RTES designers will be able to used formal methods analyze every detail of system status and requirements. Furthermore, tested models will be directly replaced by their real counterparts, so that instantaneous transition from modelling to development can take place.

The proposed simulation-based development framework overcomes the design deficiencies that we found in other design methods. Our methodology covers every aspect of the RTES design and provides a consistent design framework throughout the entire development lifecycle. Early design models will no longer be abandoned at the development phase. Rather, they are directly applied to the implementation, as our approach creates a seamless transition from modelling to development. Furthermore, the automation of the transition from model definition to real-time execution eliminates source level coding and ad-hoc program tailoring, and thus reduces the design efforts.

The proposed methodology also provides a sound mechanism for system verification. Since the DEVS formalism is derived from formal mathematical methods, the DEVSbased system design can be formally validated against the target system's specification. In addition, since the DEVS models are modular, subcomponents of larger models can be validated individually. Moreover, when the validated models are translated to RT executives running in the real world, their behaviours can also be easily verified by comparing the execution results with that obtained in the simulated world. If the two results fail to agree, the simulated solution can be revised in the simulated world for retest. If, on the other hand, a subcomponent is verified in the real world, it can be replaced by real hardware. This technique enables incremental transition from the simulated models to the actual hardware counterparts. As a result, all the subcomponents of the system-under-develop are formally verified when the development is finally finished.

#### **1.1 Contributions**

The DEVS real-time execution engine plays an important role in the proposed methodology. The design starts entirely in the simulated world. However, with the help of the execution engine, the simulated models can be executed in the real world environment. This is one of the major differences between our method and the traditional M&S methodology. This work focused on developing the DEVS real-time execution engine.

- We developed an embedded toolkit called **Embedded CD++** (**E-CD++**). E-CD++ integrates the execution of DEVS models with hardware surrogates and allows the simulated models to interact with other real components in a real-time embedded environment.

- The model execution by E-CD++ complies with the **RT-DEVS** (**Real-Time DEVS**) specification. **RT-DEVS** is a real-time extension of the DEVS formalism. It provides a sound theoretical foundation for modelling **RT** systems. Furthermore, it provides a framework for the construction of hierarchical models in a modular manner, allowing for model reuse and reducing development time and testing. It also allows hierarchical decomposition of the model by defining a way to couple existing DEVS models.

- Performance is an important factor for the success of E-CD++, because it must execute the DEVS models in real-time. We devoted lots of efforts to improve the performance of E-CD++. We implemented a technique that simplifies the model hierarchy while preserving the original model relations. By simplifying the model hierarchy, E-CD++ reduces the runtime overhead incurred by the traversal of the hierarchy. We also did the mathematical analysis on performance improvements of this technique.

- Since E-CD++ runs in the real world, we implemented wall-clock time in E-CD++. So, the activities run by E-CD++ are measured against the physical time. This is another difference between E-CD++ and other DEVS simulation toolkits, which use virtual time for simulation.

- E-CD++ also supports DEVS graphical notations; so, DEVS models generated by the graphical modelling tool can be directly executed in E-CD++.

#### **1.2 Thesis Organization**

The rest of this work is organized as follows:

Chapter 2 reviews the state-of-the-art in the M&S field. The chapter surveys the existing M&S technologies used in RTES field. It then describes the specifications of DEVS, P-DEVS, and RT-DEVS. It also provides a brief survey on the DEVS-based toolkits existing today. We conclude, based on the review of the state-of-the-art, that no M&S methodologies or toolkits exists today that is adequate to develop RTES formally. We, therefore, develops E-CD++ which servers as the DEVS RT executive in our new methodology.

Chapter 3 discusses the functionalities of E-CD++. The discussion covers four major functionalities: GGAD graphical notation, P-DEVS realization, Flattened Coordinator technique, and finally the realization of Time Interval Function.

Chapter 4 reveals the design and implementation details of E-CD++. It provides a software architecture overview, followed by the detailed descriptions of four major software modules: the Main Simulator, modelling subsystem, simulation subsystem, and messaging subsystem.

Chapter 5 is a case study in which we put all the pieces together to show how E-CD++ is used in the new methodology to develop a real application. The development of an AMS is demonstrated in detail. The case study illustrates step-by-step how the AMS is designed using hardware-in-the-loop. In addition, the experimental results are used to test the E-CD++ functionalities including GGAG graphical modelling, performance improvements by Flattened Coordinator, and P-DEVS' confluent functions.

Finally Chapter 6 states the conclusions of this work and outlines the possible future work.

## Chapter 2 M&S for Embedded Systems Design

This chapter explores the state-of-the-art in the use of M&S for embedded systems design. Many different M&S methodologies exist for embedded systems. We will survey on these methodologies and compare their strengths and limitations. From there, we will aim to find the best methodology for the RTES development. We will first provide an exposure to DEVS (Discrete EVent Systems Specification), an M&S formalism that supports hierarchical and modular modelling. We will show both the strengths and the limitations of DEVS. Then we will introduce Parallel DEVS, which is an extension to DEVS, and how it can overcome those DEVS limitations. Thirdly, we will introduce another DEVS extension called Real-time DEVS. It provides a formal modelling framework for real-time DEVS can be realized based on Parallel DEVS. Finally, to make use of DEVS models in embedded systems design, DEVS simulators must be developed. At the end of this chapter, therefore, a brief survey on the existing DEVS-based simulation toolkit will be given.

#### 2.1 M&S Methodologies

As the results of the increasing embedded systems design complexity and the shortening of the time-to-market design window, two revolutionary changes have emerged in this field [Ern98]. First, the concurrent design of hardware and software has displaced the traditional sequential design. Further, hardware and software design begins before the system architecture, or even the specification, is finalized. As a result of these changes, M&S have become a very important step in embedded systems design [CEP99].

This section provides a survey on various existing M&S methodologies for modelling embedded systems. The M&S process, in general, begins with defining the constraints imposed on the system under design, for example constraints on cost, performance, and physically dimensions. An **experimental frame** captures these constraints. Within the constraints, the M&S process captures the features of the system under design and describes its functionality. In this step, entities are identified, and an abstract representation, a **model**, is constructed. Once the model is constructed, it needs to be executed. This is done by a **simulator**, which consists of a computer system that executes the model's instructions to generate its behaviour. To complete the cycle, the results obtained are compared to those of the real system for model validation.

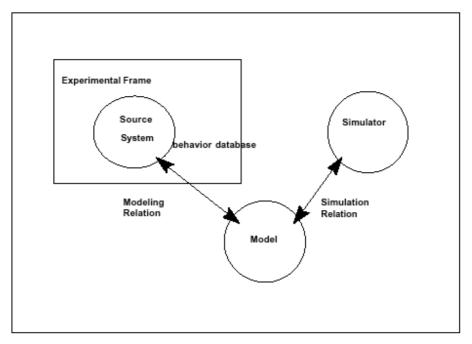

Figure 1 The basic entities and their relationships [Zei00]

The basic entities are linked by two relations [Zei00] (Figure 1):

□ *modelling relation*. Links the real system and model, defining how well the model represents the system or entity being modeled. In general terms a model can be considered valid if the data generated by the model agrees with the data produced by the real system in an experimental frame of interest.

□ *simulation relation*. Links the model and simulator. It represents how faithfully the simulator is able to carry out the instructions of the model.

Several M&S methodologies have been used for creating embedded systems. A brief description of a non-comprehensive list is given below.

- Unified Modelling Language (UML). UML is a standardized specification language for object modelling. UML is a widely adopted general-purpose modelling language that includes a graphical notation used to create an abstract model of a system, referred to as a UML model. UML provides a suite of methods that are well suited for generic software construction. However, while UML is a widely adopted methodology to model software architecture, it is neither adequate nor intended to be used to design hardware components. Therefore, UML may not be suitable for software-hardware codesign [Mar02]. Another drawback of the UML model is the lack of formal proofs of its correctness; so validation and verification efforts become non-trivial, especially for complex UML models.

- UML for Real-Time (UML-RT). UML-RT is an extension of UML. It offers additional modelling constructs based on Real-time Object-Oriented Modelling, such as event, action, resource, and schedule. UML-RT is targeted for modelling complex, event-driven, and distributed real-time systems [HS04]. However, UML-RT does not fundamentally solve the limitations inherited from the original UML. First, UML-RT supports concurrency to the same extent as defined by UML. An important shortcoming of this is the inability to guarantee processing of events using priority settings [HS04]. Secondly, UML-RT does not provide formal simulation algorithms it simply executes the models' logical specifications which undermines having a well-defined relationship between model specifications and model simulations. Moreover, UML-RT runs on top of the target system's real-time operation system (RTOS). Consequently, the resolution of time and the multi-task schedule are dependent on the underlying RTOS.

- Finite State Machines (FSM). FSM is well known for describing control systems [CEP99]. This model consists of a set of states, a set of inputs, a set of outputs, a function which defines the outputs in terms of inputs and states, and a next-state function. FSM do not allow concurrency of states, nor does it support

hierarchical constructions. Another shortcoming is the exponential growth of the number of states as the system complexity rises. Nevertheless, a number of extensions and variations of FSM have been proposed attempting to overcome the weakness of FSM. **Statecharts**, with its commercially available simulator **StateMate** [Har96], is the most widely adopted FSM extension for modelling embedded systems. Statecharts have the structure of finite-state automata enhanced with three important features: hierarchy, concurrency, and broadcast communication. One of the disadvantages of Statecharts employs UML to specify models, as opposed to using formal models. This may make the synthesis process difficult, as synthesis can be applied only if the precise mathematical meaning of a design description is applied [SLS00]. Also, Statecharts do not formally specify explicit timing, which is an important aspect in embedded systems.

- **Dataflow Graphs**. A dataflow graph consists of a set of compute nodes and directed links connecting them representing the flow of data [Alu03]. Dataflow graphs are quite popular in modelling data-dominated systems, such as signal processing [LDNA03]. While dataflow graphs are well capable of modelling dataflow systems, their semantics, however, do not well support event-driven reactive systems [Ern98].

- MATLAB. MATLAB is a simulation toolkit (<u>http://www.mathworks.com</u>), which provides a technical computing and data analysis development platform for system designers. It features integrated tools that provide user access to its math, analysis, visualization, and programming capabilities. MATLAB was built upon solid mathematical schematics. It is often used to solve differential equations and/or provide Fourier transformations. Therefore, MATLAB is suitable for modelling **Continuous Variable Dynamic Systems** (**CVDS**), whose behaviours can be best described and studied by differential equations. For instance, [RCL00] used MATLAB to model and simulate Neuro-Fuzzy systems, in which differential equations and Fourier Transformation functions were used

for the modelling. MATLAB has its limitations as well. It cannot adequately model discrete event systems, such as event-driven reactive systems and dataflow systems, where differential equations are inadequate to serve as the modelling schematics. Another limitation is that MATLAB is unable to adequately perform when many objects existed in the model [JRH03], limiting its ability to model large complex systems.

Discrete Event Simulation. In contrast to CVDS, Discrete Event Dynamic Systems (DEDS) are systems whose variables are discrete and whose time advance is continuous. Simulation mechanisms for DEDS systems assume that changes of state will take place at discrete points of time, upon the occurrence of an event. An event is a change of state that occurs at a specific point of time t<sub>i</sub> ∈ R. The occurrences of events are asynchronous. In between event occurrences, states of DEDS are unaffected.

Due to the nature of digital computing, most of the embedded systems are DEDS. Therefore, DEDS simulation is well capable of describing embedded systems. This is the primary reason why our research adopted discrete event simulation as our M&S methodology.

**Discrete event simulators** are concurrent software that simulate DEDS. Communication between processes in DE simulators is accomplished by **message passing**. A message is an artificial event that occurs in some instance of physical time. Thus, each message has an event's value and is marked with a time stamp. Each process in a DE simulator is executed when it receives a message (i.e., input events) and produces output events (messages) with the same (zero delay) or a larger time tag. The order of execution of multiple processes that have events at the same time is unspecified. Different DE simulators resolve this problem in different manner. Thus, [SLS00] states that the DE model is ambiguous, in case of simultaneous events. Although using M&S to design RTES has a promising potential [CEP99], this survey shows that none of the surveyed methodologies is perfect for RTES development. However, due to the DEDS nature of the RTES, Discrete Event Simulation seems to be most suitable for RTES. Our focus, therefore, becomes to find the solution to resolve Discrete Event Simulation's limitation on ambiguity, to make it adequate for modelling RTES. That is, we want to find a discrete event modelling formalism that gives the modeller the full control of defining a deterministic behaviour of the model upon the occurrence simultaneous events.

#### 2.2 The Original DEVS formalism

**DEVS** (**Discrete EVents Systems Specification**) [Zei76, Zei00] is a Discrete Event Simulation formalism for modelling and simulating DEDS systems. In DEVS, a model is specified as a black box with a state and a duration for that state. When the duration time for the state expires, an output event is sent, an internal transition takes place and the model changes its current state. A change of state can also occur when an external event is received. Then, a complete model is defined by describing the set of states a model goes through, the internal and external transition functions, the output function, and the state duration function. DEVS models can be put together by linking the outputs of a model to inputs of other models to form **coupled models**. Models made out of only one component are called **atomic models**.

DEVS not only proposes a framework for model construction, but also defines an **abstract simulation** mechanism that is independent of the model itself. This mechanism is high level description of how the simulation of DEVS models should be executed by a **simulator**. Two kinds of **simulators** are defined, one for atomic and another one for coupled models, this latter known as a **coordinator**. These simulators progress through the simulation by exchanging messages as described by the abstract simulation mechanism.

A real system modeled using DEVS can be described as a composition of *atomic* and *coupled* components. An **atomic model** (**M**) is defined by:

$M = \langle X, S, Y, \delta_{int}, \delta_{ext}, \lambda, ta \rangle$

where

| X                                                         | is the set of external events;                                      |

|-----------------------------------------------------------|---------------------------------------------------------------------|

| Y                                                         | is the set of internal events;                                      |

| S                                                         | is the set of sequential states;                                    |

| $\delta_{\text{ext}}: \mathbf{Q} \times X \to \mathbf{S}$ | is the external state transition function;                          |

|                                                           | where Q = { (s,e) / $s \in S$ , $e \in [0, ta(s)]$ } and $e$ is the |

|                                                           | elapsed time since the last state transition.                       |

| $\delta_{\text{int}}:S\to S$                              | is the internal state transition function;                          |

| $\lambda: S \to Y$                                        | is the <i>output function</i> ;                                     |

| ta: $S \rightarrow R_0^+ U \infty$                        | is the <i>time advance function</i> ;                               |

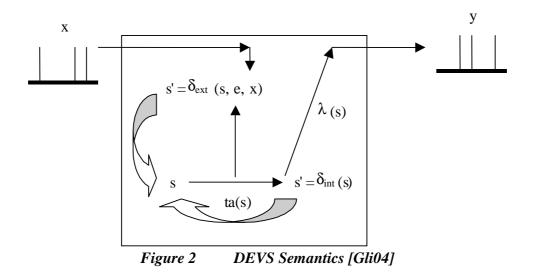

A DEVS model is in a state  $s \in S$  at any given time. In the absence of external events, it remains in that state for a lifetime defined by ta(s). A transition that occurs due to the consumption of time indicated by ta(s) is called an **internal transition**. When ta(s) time expires, the system outputs the value  $\lambda(s)$  and then changes to a new state given by  $\delta_{int}(s)$ . On the other hand, an **external transition** occurs due to the reception of an external event. In this case, the external transition function determines the new state, given by  $\delta_{ext}(s, e, x)$  where *s* is the current state, *e* is the time elapsed since the last transition and  $x \in X$  is the external event that has been received.

The time advance function can take any real value between 0 and  $\infty$ . A state for which ta(s) = 0 is called a **transient state**. In contrast, if the  $ta(s) = \infty$  then s is said to be a **passive state**, in which the system will remain perpetually unless an external event is received.

The following figure in [Gli04] shows the description of states and variables in DEVS models:

A DEVS **coupled model (CM)** is composed of several atomic or coupled submodels. It is formally defined by:

$$CM = \langle X_{self}, Y_{self}, D, \{M_i\}, \{I_i\}, \{Z_{ij}\}, select \rangle$$

where

*D* Is a set of components;

for each *i* in *D*,

$M_i$  is a *basic DEVS component* (*i.e.* a coupled or atomic model); for each *i* in *D U* { *self* },

*I<sub>i</sub>* is the *set of influencees* of *i* (*i.e.* models that can be influenced by outputs of model *i*);

for each j in  $I_i$ ,

$Z_{i,j}$  is the *i-to-j output-input translation* function Select is the *tie-breaker* function;

This structure is subject to the constraints that for each i in D,

$M_i = \langle X_i, Y_i, S_i, \delta_{i int}, \delta_{i ext}, \lambda_i, ta_i \rangle$  is a DEVS model

$I_i$  is a subset of  $D \cup \{ self \}, i$  is not in  $I_i$ .

$Z_{self, j}: X_{self} \to X_{j}$   $Z_{i,self}: Y_{i} \to Y_{self}$   $Z_{i,j}: Y_{i} \to X_{j}$ select: subset of D  $\to$  D

such that for any non-empty subset E, select (E)  $\in$  E.

A *coupled model* groups several DEVS into a compound model that can be regarded, due to the closure property, as a new DEVS model. This allows hierarchical model construction.

In addition, each *coupled model* has its own input and output events, as defined by the  $X_{self}$  and  $Y_{self}$  sets. When external events are received, the coupled model has to redirect the inputs to one or more components. Similarly, when a component produces an output, it may have to map it as an input to another component, or as an output of the coupled model itself. Mapping between ports is defined by the *Z* function.

Two types of ambiguities may rise in DEVS simulations. The ambiguity rises when multiple components are scheduled for internal transitions at the same time in a coupled model. The way the DEVS formalism solves this ambiguity is by the use of the *select* function. The function defines an order over the components so that only one component of the group of imminent models is allowed to have e = 0. The other imminent models are divided in two groups: those that receive an external output from this model, and the rest. The former will execute their external transition functions with e = ta(s), and the latter will be imminent during the next simulation cycle which may require again the use of the select function to decide which model will execute first. This tie-breaking approach, however, is a potential source of errors since the serialization produce may not reflect the correct system's behaviour upon the occurrence of simultaneous events.

The second type of the ambiguities may rise in an atomic model when it receives an external event at the exact time when an internal transition is scheduled. It is not clear which transition this model should execute first, for the DEVS formalism does not

specify the order. So, two alternatives exist: to execute the external transition first with e = ta(s) and then the internal transition, or else to execute the internal transition first followed by the external transition with e = 0. It is up to the simulation software to decide which alternative to choose. This serialization constraint, however, may again cause errors.

#### 2.3 Parallel DEVS Formalism

While the DEVS formalism suffers from its serialization constraints, the **Parallel DEVS** (**P-DEVS**) formalism [Cho94a] was introduced to resolve this issue. A **P-DEVS model** is described as a set of basic and coupled models. In addition, the model's interface was also revised. A model will now have input and output ports through which all interaction with the environment takes place. Events determine values appearing on such ports. A model receives outside events through its input ports. Upon reception of such events, the model description must determine how it responds to them. In addition, internal events arising within the model change its state, and manifest themselves as events on the output ports to be transmitted to other model components.

Atomic models are still the most basic constructions, which can be combined with other models into coupled models. A Parallel-DEVS coupled model satisfies the closure property [Cho94b], so it can be seen as another basic model. Therefore, Parallel-DEVS preserves the hierarchical properties of the original DEVS formalism.

The **P-DEVS atomic model** has the following structure:

$$M = \langle X_M, Y_M, S, \delta_{ext}, \delta_{int}, \delta_{con}, \lambda, ta \rangle$$

where

$X_M = \{(\mathbf{p}, \mathbf{v}) | \mathbf{p} \in IPorts, \mathbf{v} \in X_p\}$  is the set of *input ports and values*;  $Y_M = \{(\mathbf{p}, \mathbf{v}) | \mathbf{p} \in OPorts, \mathbf{v} \in Y_p\}$  is the set of *output ports and values*; S is the set of *sequential* states;

$\delta_{ext}: Q \ge X_M^{b} \rightarrow S$  is the external state transition function;

$\delta_{int}: S \rightarrow S$  is the internal state transition function;

$\delta_{con}: Q \ge X_M^{b} \rightarrow S$  is the confluent transition function;

- $\lambda: S \to Y_M^{b}$  is the *output function*;

- $ta: S \rightarrow R_{o}^{+} \cup \infty$  is the time advance function;

with  $Q := \{ (s, e) \mid s \in S, 0 \le e \le ta(s) \}$  the set of total states.

The semantics of the P-DEVS definition are as follows. At any given time, a basic model is in a state *s*. And in the absence of external events, it will remain in that state for a period of time as defined by ta(*s*). When an internal transition takes place, the system outputs the value  $\lambda(s)$ , and changes to state  $\delta_{int}(s)$ . If one or more external events  $E = \{x_1 \\ ... \\ x_n / x \in X_M \}$  occurs before ta(*s*) expires, i.e., when the system is in the state (s, e) with  $e \leq ta(s)$ , the new state will be given by  $\delta_{ext}(s, e, E)$ . Suppose that an external and an internal transition collide, i.e., an external event *E* arrives when e = ta(s), the new system's state could either be given by  $\delta_{ext}(\delta_{int}(s), e, E)$  or  $\delta_{int}(\delta_{ext}(s, e, E))$ . The modeler can define the most appropriate behavior with the  $\delta_{conf}$  function. As a result, the new system's state will be the one defined by  $\delta_{conf}(s, E)$ .

#### A P-DEVS coupled model (CM) is defined by:

$$CM = \langle X, Y, D, \{M_d | d \in D\}, EIC, EOC, IC \rangle$$

where

$X = \{(p,v) | p \in IPorts, v \in X p \}$  is the set of input ports and values;

$Y = \{(p,v) | p \in OPorts, v \in Y p\}$  is the set of output ports and values;

$M_d$  is a set of atomic models, and D is a set of the atomic models' names, where

for each  $d \in D$

$$M_{d} = (X_{d}, Y_{d}, S, \delta_{ext}, \delta_{inb}, \delta_{con}, \lambda, ta) \text{ is a DEVS basic structure}$$

with  $X_{d} = \{(\mathbf{p}, \mathbf{v}) | \mathbf{p} \in IPorts, \mathbf{v} \in X_{p}\};$

$Y_{d} = \{(\mathbf{p}, \mathbf{v}) | \mathbf{p} \in OPorts, \mathbf{v} \in Y_{p}\};$

The couplings are subject to the following conditions:

• *external input couplings (EIC)* connect external inputs to component inputs:

$EIC \subseteq \{((N, ip_N), (d, ip_d)) \mid ip_N \in IPorts, d \in D, ip_d \in IPorts_d\}$

• *external output couplings (EOC)* connect component outputs to external outputs:  $EOC \subseteq \{((d, op_d), (N, op_N)) | op_N \in OPorts, d \in D, op_d \in OPorts_d\}$

• *internal couplings (IC)* connect component outputs to component inputs:

$IC \subseteq \{((a, op_a), (b, ip_b)) \mid a, b \in D, op_a \in OPorts_a, ip_b \in IPorts_b\}$

No direct feedback loops are allowed, i.e., no output port of a component may be connected to an input port of the same component i.e.,

$((d, op_d), (e, ip_d)) \in IC$  implies  $d \neq e$ .

• Range inclusion constraints: the values sent from a source port must be within the range of accepted values of a destination port, i.e.,

$\forall ((N, ip_N), (d, ip_d)) \in EIC : X_{ipN} \subseteq X_{ipd}$   $\forall ((a, op_a), (N, op_N)) \in EOC : Y_{opa} \subseteq Y_{opN}$   $\forall ((a, op_a), (b, ip_b)) \in IC : Y_{opa} \subseteq X_{ipb}.$

Comparing with DEVS, P-DEVS has the following 2 capabilities that DEVS lacks of:

- Be able to give the modeller a complete control over the collision behaviour when

a component receives events at the time of its internal transition via the use

confluent function δcon. This function will define a new model's state when there

is a collision between internal and external transitions. Basically, this function

will allow the modeller to specify how the model should behave in the presence of

collisions.

- Be able to eliminate the necessity for tie-breaking simultaneously scheduled events, which is done by the SELECT functions in DEVS. In P-DEVS, the external and output functions no longer handle one event at a time. Instead, bags of events are now being handled, allowing then for simultaneous processing of multiple events. In other words, P-DEVS provides parallel activation of all imminent children of a coupled model.

## 2.4 Real-time DEVS (RT-DEVS) Formalism

The **RT-DEVS** [HSKP97] is a formalism for real-time discrete event systems modelling. It is an extension of the DEVS formalism that provides a seamless framework for the development of real-time control software that includes modelling, design, analysis, simulation, and implementation. The RT-DEVS has additional specifications that are not in the original DEVS formalism: the time interval function and the weak synchronization communication mechanism [SK05]. Since in real-time systems, an event occurrence time may not be an exact value but an interval, the time advance in RT-DEVS is given by a time interval. An atomic model in RT-DEVS formalism, RTAM, is given by the following seven-tuple [SK05]:

$$RTAM = \langle X_M, Y_M, S, \delta_{ext}, \delta_{int}, \delta_{con}, \lambda, ti \rangle$$

$$ti: S \rightarrow R_0^+ \ge R_0^+ where ti(s)|_{min} \le ta(s) \le ti(s)|_{max}, s \in S$$

Note that RTAM is the same as the original DEVS atomic model, expect that the time advance function is replaced by the time interval function *ti*.

The definition of coupled models defined by RT-DEVS is the same as that defined by P-DEVS.

The DEVS formalism does not explicitly define a communication mechanism between components coupled together. The RT-DEVS, by contrast, explicitly defines the communication mechanism, called *weak synchronization*. It has two characteristics:

- Concurrency on simultaneously scheduled events. For example, suppose there are two real-time atomic models A and B, and A's output port is connected to B's input port. As a result, A's output function generates an external event to B. In RT-DEVS, A's internal transition and B's external transition takes place concurrently.

- Synchronization loss: A real-time component that is trying to make an internal transition should not block other components that are not ready for synchronization. For example, suppose that atomic models A and B have no

connections via any ports. Then A's internal transition changes its state alone. That is, B's state remains unchanged, causing synchronization loss.

In practice, the implementation of P-DEVS provides weak synchronization, because it provides concurrent activation of all imminent children of a coupled model, and also because it also guarantees synchronization loss [Cho94a]. Therefore, the RT-DEVS formalism can be constructed by implementing both the time interval function and P-DEVS.

#### 2.5 Applying DEVS to Embedded Systems Design

DEVS technology has been usually applied to large-scale dynamic systems, with implementations running on workstations and servers. As these systems focus on the high level modelling and simulation, another branch of DEVS application is on real-time event-based control [HZC01]. These low level applications exist largely on embedded systems, which are usually characterized as "intelligent devices" consisting of computer hardware and real-time software. This work mainly studies how to use DEVS technology to design real-time embedded systems.

Comparing with serial DEVS, P-DEVS is a major advance in modelling real-time systems, because it provides an appropriate basis to develop simulation models exhibiting concurrent behaviour. However, while P-DEVS provides sound modelling principles to characterize structural and behaviour aspects of real-time systems, recent research suggests that transforming (or mapping) DEVS models to actual designs of real-time embedded systems is non-trivial [HS04].

Recent research, therefore, has been focusing on developing schemes to support the transformation from simulation modelling to designs of real systems. One attempt was the DEVS-on-a-chip approach, which implements DEVS on a microprocessor that has limited memory and processing ability [HZC01]. It creates a just-as-needed real time environment. This effort, however, did not implement a full scale of RT-DEVS

specifications on the chip. As a result, it only demonstrates the capability of creating realtime embedded systems that have relatively simple compositions.

Another research effort in this area focused on how to use RT-DEVS as a framework to develop hardware-in-the-loop applications [LPW03]. These applications are complex as a result of the high degree of interaction between software and hardware components. Therefore, the development of these applications is a challenging process in which M&S can become essential. The technique of applying RT-DEVS to develop hardware-in-the-loop applications seamlessly integrates simulation models with hardware components and also enables incremental transition from the simulated models to the actual hardware counterparts.

#### 2.6 DEVS-based simulation toolkits

Prior to this work, many DEVS-based toolkits have already been developed by different research groups. A brief survey on these tools has been given by [Gli04] as follows:

- ADEVS [Nut06] supports the construction of discrete event models based on a variant of the P-DEVS formalism. It includes support for dynamic structure models based on the Dynamic DEVS formalism [Uhr01a].

- DEVS-C++ [Zei06] is a high performance simulation environment that allows portability of models across platforms at a high level of abstraction. It uses a set of C++ classes, called containers, to implement serial and parallel simulation.

- DEVS-Scheme [Zei93] is a knowledge-based environment implemented in Scheme for discrete-event model construction and simulation. It allows combining symbolic and hierarchical, modular discrete-event modelling approaches.

- DEVS/HLA [Zei99b] is an HLA-compliant M&S environment implemented in C++ that supports high level model construction. It greatly simplifies the underlying programming details required to establish and participate in an HLA federation.

- DEVS/Grid [Seo04] is an M&S framework implemented using Java and Globus toolkit for Grid computing infrastructure.

- DEVSCluster [Kim04] is a CORBA-based, multi-threaded distributed simulator implemented in Visual C++. It transforms a hierarchical DEVS model into a non-hierarchical one to ease the synchronization of the distributed simulation.

- DEVSJAVA [Sar98] is a DEVS-based Simulator that supports high-level modelling.

- GALATEA [Dav00] is offered as a family of languages to model multi-agent systems to be simulated in a DEVS multi-agent platform.

- JDEVS [Fil02] is an M&S environment that enables discrete-event, general purpose, object-oriented, component-based, GIS, (Geographic Information System) connected, collaborative, visual simulation model development and execution.

- JAMES [Uhr01b] is a Java-based simulation environment that allows the modeler to describe agents and their environment as situated automata.

- PyDEVS is a simulator developed in ATOM3 [Del02], a tool for multi-paradigm modelling. DEVS models are constructed using the ATOM3-DEVS tool, which generates Python code to be executed with the PyDEVS simulator.

- PowerDEVS [Kof03] is an M&S toolkit developed in C++ for hybrid systems. Atomic DEVS models can be graphically coupled in hierarchical block diagrams to create complex systems.

- SimBeans [Pra99] is a discrete-event simulation framework based on DEVS and the JavaBean component model.

- CD++ [Rod99, Wai02a] is an M&S toolkit developed in C++ that implements the original DEVS formalism.

None of the toolkits listed above, however, is capable of applying RT-DEVS to real-time embedded systems design using hardware-in-the-loop. The aim of this work is to create such a toolkit. To do so, our strategy is to reuse some of the existing CD++ software components and build new functionalities as necessary. The resultant toolkit is the

Embedded CD++ (E-CD++). In general, CD++ and E-CD++ have the following major differences:

- CD++ implements DEVS, whereas E-CD++ implements RT-DEVS (i.e., P-DEVS combined with the Time Interval Function).

- CD++ runs on workstations, whereas E-CD++ runs on a single board computer (SBC).

- CD++ uses logical time, whereas E-CD++ supports both logical and physical clock.

- E-CD++ has better simulation performance than CD++, since E-CD++ implemented a Flattened Coordinator technique to improve the performance.

- CD++ does not interact with real-world events, whereas E-CD++ does. It uses the input ports on the SBC to receive events from real input devices, such as sensors and timers. As well, the outputs can be sent through output ports connected to devices, such as motors and gears.

- CD++ can only simulate homogenous DEVS models, where as E-CD++ can seamlessly integrate DEVS components with hardware components.

- E-CD++ supports graphical modelling, which is a new functionality that CD++ does not have.

#### 2.7 M&S Methods for RTES Design

In the past, M&S have been used to model and simulate the system under study, so that the system behaviour can be analysed and examined. M&S was used only to study the target system in a simulated environment. This work, however, attempts to apply the M&S methodology directly to the design of the target system.

Using M&S to design real-time embedded systems has a promising potential. [Ern98] stated the importance of Modelling in modern embedded system design, and [SLS00] further claimed that formal models are essential to embedded system design. However, defining a formal modelling methodology that is adequate in modelling all kinds of embedded systems is a challenge. We found that some models, such as FSM, support

event-driven reactive systems, while others target dataflow systems. A combination using both domains (e.g., telecom devices) implies simulation overhead. As well, some simulators, such as MATLAB, are adequate in modelling CVDS, but not suitable for DEDS. Due to their digital nature, embedded systems can be categorized as DEDS. Consequently, we found that RT-DEVS is an adequate state-of-the-art modelling methodology for embedded systems. Furthermore, recent advancement of the DEVS research has extended DEVS to a new embedded system design paradigm in which RT-DEVS is used as a framework that seamlessly integrates simulation models with hardware components and that also enables incremental transition from the simulated models to the actual hardware counterparts.

However, although RT-DEVS is adequate in *modelling* embedded systems, no simulation toolkit available can apply RT-DEVS directly to the *implementation* of the target system. Modelling and implementation differ in the way that, in modelling, all models (including hardware models) are simulated software components, while implementation must integrate hardware and software components. In other words, implementation must face the hardware/software partition problem, implying that no instantaneous transition exists from the modelling phase to the implementation phase.

The aim of E-CD++ is to address this issue. Since the hardware/software partition problem is NP-complete, no formal methodology can be found to solve this problem. Therefore, imperial approach has to be used instead. The E-CD++ toolkit merges the RT-DEVS formalism with hardware-in-the-loop design methodology. That is, E-CD++ creates an real-time execution environment which integrates RT-DEVS models with real hardware components. In this way, RT-DEVS is directly applied to the implementation of the system under design.

## Chapter 3 Embedded CD++ (E-CD++)

In this chapter, we introduce the Embedded CD++ (E-CD++) toolkit. We first give a brief introduction to CD++ and E-CD++. We then extend our discussion to exploring four major functionalities of E-CD++: a GGAD (Generic Graphic Advanced environment for DEVS modelling and simulation) interpreter, P-DEVS simulation, the Flattened Coordinator technique, and the Time Interval Function. With the realization both P-DEVS and the Time Interval Function, E-CD++ carries out RT-DEVS simulation. Finally, performance is a critical attribute for an embedded simulator that performs realtime simulations. E-CD++ adopts the Flattened Coordinator technique to improve its performance. We provide a theoretical discussion on E-CD++ performance when exploring the Flattened Coordinator technique.

#### 3.1 CD++

Not only does DEVS propose a framework for model construction, it also defines an abstract simulation mechanism that is independent of the model itself. This mechanism provides a high level design on DEVS framework, and it can be feasibly implemented by computer software. **CD**++ [Wai02] is a simulation software which implements the DEVS simulation formalism. In CD++, two kinds of **simulators** are implemented, one for atomic and the other for coupled models. The latter is known as a **coordinator**. These simulators progress through the simulation by exchanging messages as described by the abstract simulation mechanism.

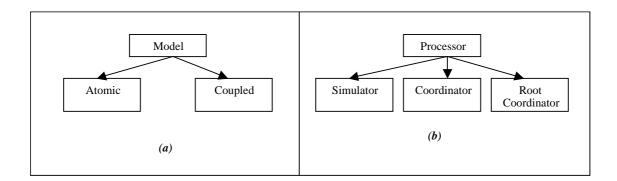

**CD**++ is written in C++. Two basic abstract classes exist: Model and Processor. The former is used to represent the behaviour of the atomic and coupled models, while the latter implements the simulation mechanisms. Figure 3 shows the CD++ class hierarchy.

Figure 3 CD++ (a) Model hierarchy, (b) Processor hierarchy

The user-defined DEVS models are subclasses derived from the Model class, which defines the model states and the internal and external state transition functions. CD++ also allows the user to create a model file which defines the model hierarchy and linkage between ports.

Message passing are among Processor objects, which upon receiving certain messages, trigger the appropriate state transition functions.

# 3.2 E-CD++

CD++ was developed to run in a simulated environment carrying out only simulated results. E-CD++, by contrast, is developed to apply the RT-DEVS formalism to embedded systems design which requires real-time expansion and interact on the surrounding environment. The inputs of E-CD++ can be received by ports connected to real input devices such as sensors, timers, thermometers, or data collected from human interaction. The outputs can be sent through output ports connected to devices such as motors, transducers, gears, valves, or any other component.

E-CD++ runs on a Single Board Computer (SBC). It supports hardware-in-the-loop simulations by developing hybrid hardware/software systems -- integrations of simulated software models and real hardware components [LPW03].

The DEVS model is then loaded onto the SBC running E-CD++ for validation. E-CD++ supports RT-DEVS in which time advancement is driven by the wall-clock. Furthermore, the inputs and outputs ports on the SBC are real hardware that is used by the E-CD++ to let the DEVS model interact with the environment. E-CD++ can also integrate simulation models with hardware components, which enables incremental transition from the simulated models to the actual hardware counterparts.

The testing results obtained on the SBC can be compared with the simulation results obtained on the host workstation. If the two results do not agree, then the DEVS model or the event file developed on the workstation can be easily modified or adjusted to obtain more accurate results.

E-CD++ inherits all the functionalities of the original CD++, while adding the following new functionalities:

- Supports the GGAD graphical modeller;

- Implements RT-DEVS by implementing the P-DEVS formalism and the time interval function;

- Implements the Flattened Coordinator technique;

- Is able to simulate DEVS models in an embedded computing environment with limited resources;

- Is able to let DEVS models respond to real world events via input and output ports of the embedded system.

# **3.3 GGAD Graphical Notation**

E-CD++ provides a graphical user interface (GUI) for modellers to specify atomic models graphically, enabling non-expert users to define atomic models in a easier and more intuitive way. The tool generates textual specifications of the models represented graphically in the GUI.

The GUI is based on a DEVS-graph notation presented in [HSKP97], which allows defining atomic models using a graphical modelling tool. An atomic model is placed

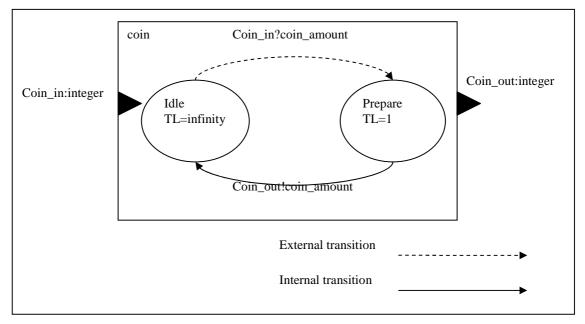

inside a box (Figure 4). An external state transition is represented by a dotted line in which the input event is represented by "?". Similarly, an internal state transition is represented by a solid line in which the output event is represented by "!". For example, an input event in?m means that a message m arrives at the input port in, and an output event out!m means that a message m is run through port out. The input and output ports are denoted by the black triangles. The atomic states are marked by circles in which the state names and the time advance functions are defined.

Figure 4 Graphical definition of an atomic model: Coin Displayer

Figure 4 is a graphical representation of an atomic model called *coin*. This model simulates the behaviour of the coins displayer in a vending machine. It has one input port, namely *coin\_in*, representing the input coins slot and one output port called *coin\_out* which represents the display of the inserted coins' amount, and the port values of both ports have integer data type. When coins are inserted into the coins slot, it takes one second for the coins displayer to display the coins' amount.

The two circles in the diagram represent the model's two internal states whose names and time intervals are defined inside the circles. The "Idle" state is the initial state of which the time interval is set to infinity, which implies that the model may remain idle if no external events (e.g., inserting coins) arrives. In contrast, the "Prepare" state has only one

second time interval, meaning that it takes one second for the "Prepare" state to change to another one. That is, when coins are inserted into the coins slot, it takes one second for the coins displayer to display the coins' amount.

The external transition function of the coins displayer is defined by the dotted arrow line in Figure 4. When a coin is inserted via the input port, the external transition function changes the model's state from "Idle" to "Prepare" and stores the input value to the local variable "coin\_amount". After one second time interval elapses, the output function, defined right below the solid arrow line, outputs the "coin\_amount" value to the output port, and the internal state transition, defined by the solid line, changes model state back to "Idle".

The textual specifications are defined by a modelling language called GGAD. A GGAD file is a text file that contains an atomic model written in GGAD. As an example, Figure 5 provides the textual definition of the atomic model represented in Figure 4.

```

[coin]

in: coin_in

out: coin_out

var : coin_amount

state: idle prepare

initial: idle

int: prepare idle coin_out!coin_amount

ext: idle prepare any(coin_in)?1 {coin_amount = coin_in;}

idle: infinite

prepare: 0:0:1:0

coin_amount: 0

```

#### Figure 5 GGAD textual definition of the coin model

This first line in the GGAD file is always the name of the atomic model encoded by the square brackets. The rest of the file content defines the model's ports, states, state transition functions, local variables used in transition functions, and time advance functions. The order of these definitions is arbitrary, and tokens in GGAD are separated by white spaces.

• The input ports (line 2) are defined by the keyword "in" followed by a colon and a list of port names separated by white spaces.

- Similarly, the output ports (line 3) are defined by the keyword "out" followed by a colon and a list of output port names.

- The local variable list (line 4) and the state list (line 5) are both followed the same syntax rule, except their responding keywords are "var" and "state" respectively.

- The keyword "initial" is used to define the initial state. For example, the initial state of the coin model (line 6) is "idle".

- The time advance function is defined by a state name followed by a colon and a GGAD time. The GGAD time has the format "HH:MM:SS:MS" For example, the elapse time of the prepare state is 1 section (line 10). In addition, the keyword "infinite" defines the passive state. In our example, the "idle" state is a passive state (line 9).

- The internal transition function is defined as follows. It starts with the keyword "int" followed by a colon. The next two tokens are the start state and the destination state. Then remainder part of the function defines the output function. The keyword "!" is the output mark. The left hand side of "!" is the output port name, and the right hand side is the output value. For example, the internal transition of coin (line 7) starts at state "prepare" and ends at state "idle". The output function outputs the value of local variable "coin\_amount" to port "coin\_out".

- The keyword "ext" denotes the start of an external transition function (line 8). The external transition function also has a start state and a destination state, which are defined in the same syntax as that defined in internal transition functions. The keyword "?" is the so-called input mark. The left hand side of "?" is a GGAD expression, while right hand side is an integer constant. Once an external event takes place, the GGAD modeller evaluates the expression and compares the result with the integer constant. If the two values agree, the GGAD modeller will execute this external transition function. Otherwise, the function will not be executed. GGAD uses this approach to select the correct external transition function to execute upon a particular external event. In our coin example, the expression "any(coin\_in)" returns 1 if a new value arrives at input port "coin\_in" and returns 0 otherwise. So, the external transition defined is line 8 will be

executed upon the event where new coins are inserted into "coin\_in". Detailed exploration on GGAD expressions will be covered in the next chapter.

The last part of the external transition function is a list of GGAD actions, enclosed by curry brackets. They form the body of the external transition function. GGAD actions are C++ assignment like statements and are separated by semicolons. In the coin model example, the GGAD action "coin\_amount = coin\_in;" assigns the input value arrived at input port "coin\_in" to the local variable "coin\_amount". GGAD actions will be discussed in the next chapter in detail.

The complete definition to GGAD grammar can be found in Appendix B: Grammar for GGAD Models.

# **3.4 P-DEVS Simulation Algorithms**

The formal definition and semantics of P-DEVS is given in Chapter 2. This section discusses the definition of P-DEVS simulation algorithms used in E-CD++. That is, we focus on how to transform the specifications of P-DEVS (written in mathematical terms) into algorithms that can be implemented by computer programs.

The P-DEVS formalism allows the modeller to specify the state transition behaviours of atomic and coupled models, as well as the port connections among models. These connections constitute the model hierarchy. The distinctiveness of P-DEVS is that it supports parallel executions on simultaneous state transitions of atomic models and concurrent handling of simultaneously scheduled external events. Moreover, handling external events from the environment, executing transition functions, and exchanging messages among models through their input and output ports that trigger more state transitions to happen constitute all the activities of P-DEVS simulations. More specifically, the following three functionalities are needed:

- 1. *Parallel executions on simultaneous state transitions*. This functionality may be achieved by periodically determining the imminent atomic models at each simulation cycle with time advancement and synchronizing their state transition activities. In E-CD++, each model has internal variables to keep the time of the simulation, as listed below.

- $t_L Time of last transition$  $t_N Time of next transition$

An **imminent atomic model's simulator** has the smallest value of  $t_N$ . among its siblings. In other words, it is a model that holds an imminent state transition that will occur in the next simulation cycle in which time will advance to the model's  $t_N$ . A simulation cycle advances time from  $t_L$  to  $t_N$ , where  $t_L$  is the end time of the previous simulation cycle and  $t_N$  is the finish time of the current cycle. Within this time period, there may be multiple imminent atomic models. With P-DEVS implementation, E-CD++ is capable of executing these state transitions simultaneously. This capability differentiates E-CD++ from the original CD++ simulator, where the SELECT functions are used to serialize the executions of these simultaneous state transitions.

To achieve parallelism on state transitions, synchronization of models' activities is necessary. The synchronization of atomic models' state transitions can be achieved by inter-component messaging. E-CD++ implements a new intercomponent messaging architecture that is very different from the original CD++ design, so that it can offer this functionality. Two main categories of messages exist: **synchronization** and **content** messages. Each of these categories consists of several types of messages.