## **Verification Methodology for DEVS Models**

By

Hesham Saadawi

A PhD thesis submitted to

The Faculty of Graduate and Postdoctoral Affairs

In partial fulfillment of

The degree requirements of

Doctor of Philosophy in Computer Science

Ottawa-Carleton Institute for

**Computer Science**

School of Computer Science

Carleton University

Ottawa, Ontario, Canada

Fall 2012

Copyright © 2012

Hesham Saadawi

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-94229-1

> Our file Notre référence ISBN: 978-0-494-94229-1

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distrbute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protege cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### Abstract

Modeling is an effective tool for studying the behaviour of a system. When modeling, the system's descriptions are usually abstracted into simpler models. These models can then be analyzed and solved (manually or automatically) by using different mathematical techniques. However, sometimes the models become too complex to analyze formally. In those cases, computer Modeling and Simulation (M&S) can help designers to understand the behaviour of these systems better. One example of such complex systems are Real-Time (RT) systems, which are usually composed of a digital computer executing software that interacts with the external physical environment with tight timing constraints.

In studying these systems, M&S has proven to be an essential tool. However, when simulating RT models, the required interactions could quickly grow beyond the ability of human observation and analysis. Instead, formal methods for verifying these systems can guarantee the correct and timely function of these systems.

Due to the benefits of formal verification of RT simulation models, this thesis introduces a methodology to enable performing formal verification of simulation models based on the Discrete Event System Specification (DEVS) formalism. The thesis introduces a road map for a complete methodology to formally verify DEVS models, thus enabling better methods for M&S validation and verification and making M&S a better tool for RT-embedded systems development.

# Acknowledgements

I'm indebted for this work to the continuous support and encouragement of my supervisor Dr. Gabriel A. Wainer. I am grateful for his time and effort in supporting my professional and personal development.

## **Table of Contents**

.

| Abstract                               | ii               |

|----------------------------------------|------------------|

| Table of Contents                      | iv               |

| List of Tables                         | vii              |

| List of Figures                        | viii             |

| Acronyms                               | xi               |

| <b>Chapter 1: Introduction</b>         | 1                |

| 1.1 Objectives                         |                  |

| 1.2 Originality of the Research        |                  |

| 1.3 Structure of the Thesis            |                  |

| Chapter 2: Survey of State of the Art  | 10               |

| 2.1 Discrete Event System Specificat   | ion (DEVS) 10    |

| 2.2 Timed Automata (TA)                |                  |

| 2.2.1 TA and Model Checking            |                  |

| 2.3 Related work on DEVS verification  | on techniques 22 |

| 2.4 Hybrid DEVS models                 |                  |

| 2.4.1 The Quantized State Systems      | (QSS) method     |

| 2.5 Introduction to Interval Arithmeti | c 42             |

| 2.6 Summary Discussion of the State-of-the-Art                         |

|------------------------------------------------------------------------|

| Chapter 3: Thesis contribution 40                                      |

| 3.1 List of Published Contributions                                    |

| Chapter 4: The RTA-DEVS formalism 54                                   |

| 4.1 Rational Time Advance DEVS (RTA-DEVS)                              |

| 4.2 Estimate of Expressiveness Difference between DEVS and RTA-DEVS    |

| 4.3 RTA-DEVS to Timed Automata Behavioural Equivalence                 |

| 4.3.1 RTA-DEVS internal transition semantics                           |

| 4.3.2 RTA-DEVS external transitions semantics                          |

| 4.3.3 An Alternative way to show bisimulation between RTA-DEVS Interna |

| Transition and TA Transition                                           |

| 4.4 An algorithm for behavioural equivalence                           |

| 4.5 Resolving rational numbers in RTA-DEVS model                       |

| 4.6 DEVS to RTA-DEVS                                                   |

| 4.7 Estimation of Approximation to Verification Results                |

| 4.8 Case study: an Elevator Control System                             |

| 4.9 Known Methodology Limits10                                         |

| Chapter 5: Hybrid DEVS Systems Verification. 10                        |

| 5.1 Continuous-Discrete systems Verification                           |

| 5.1.1 Transforming QSS DEVS models to TA                               |

| 5.1.2 Case Study of a Hybrid Elevator System                           |

| 5.1.3 Verifying general QSS                                | 128 |

|------------------------------------------------------------|-----|

| 5.1.4 Advantages of using QSS/DEVS to verify Hybrid Models | 147 |

| Chapter 6: Conclusion & Future Research                    | 148 |

| 6.1.1 Possible Future Research                             |     |

| REFERENCES                                                 |     |

.

.

.

.

•

.

# List of Tables

.

•

| Table 1: Related Work of DEVS Verification and Contribution          | 28  |

|----------------------------------------------------------------------|-----|

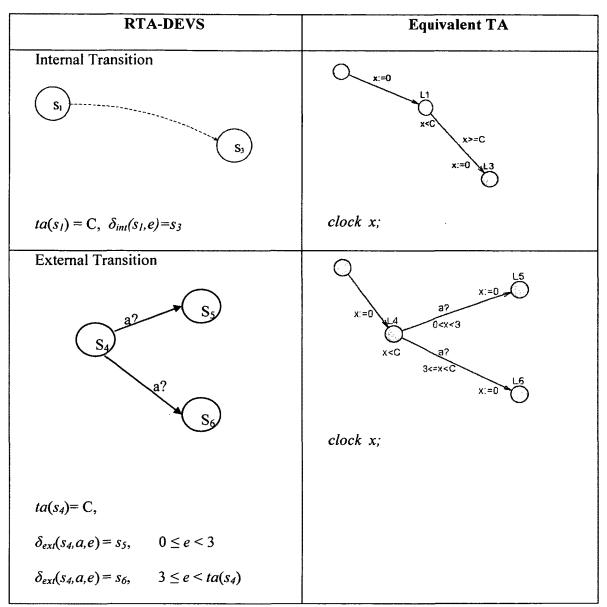

| Table 2: Transformation of RTA-DEVS to Behaviourally Equivalent TA   | 87  |

| Table 3: UPPAAL arithmetic operators                                 | 137 |

| Table 4: User defined functions for the UPPAAL TA model of figure 48 | 140 |

| Table 5: User defined functions for the UPPAAL TA model of figure 49 | 142 |

# **List of Figures**

| Figure 1: DEVS atomic component state transition sequence (extracted, with                      |

|-------------------------------------------------------------------------------------------------|

| Figure 2: DEVS Model Hierarchy 15                                                               |

| Figure 3: Timed Automaton 19                                                                    |

| Figure 4: Quantization Function with Hysteresis (extracted, with permission, from [51]).        |

|                                                                                                 |

| Figure 5: QSS Block Diagram Model                                                               |

| Figure 6: Continuous function of exponential Decay                                              |

| Figure 7: Linear approximation of Decay formula                                                 |

| Figure 8: Quantized representation of Exponential Decay                                         |

| Figure 9: Thesis Contribution                                                                   |

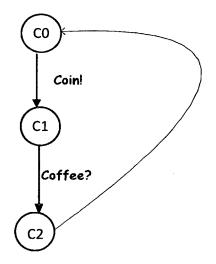

| Figure 10: Coffee-Team-Machine 1 (CTM1)65                                                       |

| Figure 11: User Behaviour                                                                       |

| Figure 12: Coffee-Team-Machine 2 (CTM2)                                                         |

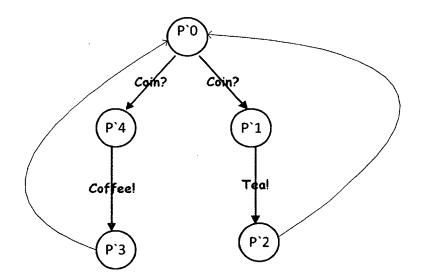

| Figure 13: (a) RTA-DEVS model. (b) Timed Automata model                                         |

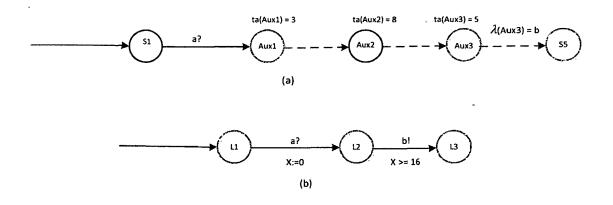

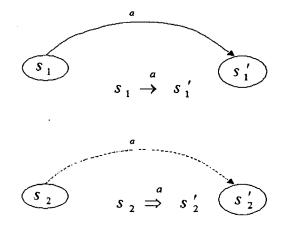

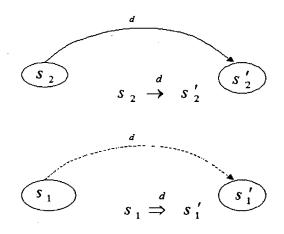

| Figure 14: Direct delay transition from $s_1$ to $s'_1$ and corresponding eventual delay        |

| transition from $s_2$ to $s'_2$                                                                 |

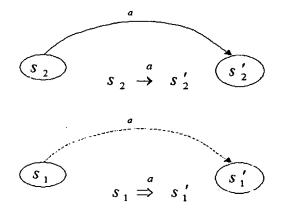

| Figure 15: Direct action transition from $s_1$ to $s'_1$ , and corresponding eventual action 72 |

| Figure 16: Direct delay transition from $s_2$ to $s'_2$ and corresponding eventual delay        |

| transition from $s_1$ to $s'_1$                                                                 |

| Figure 17: Direct action transition from $s_2$ to $s'_2$ , and corresponding eventual action 73 |

.

•

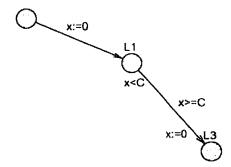

|   | Figure 18: RTA-DEVS Internal Transition.                                       | 74  |

|---|--------------------------------------------------------------------------------|-----|

|   | Figure 19: TA model for an Internal RTA-DEVS transition                        | 75  |

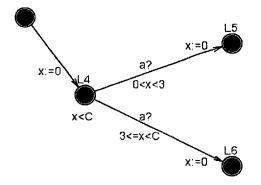

|   | Figure 20: RTA-DEVS External transitions on action a                           | 80  |

| • | Figure 21: TA model for RTA-DEVS external transition.                          | 81  |

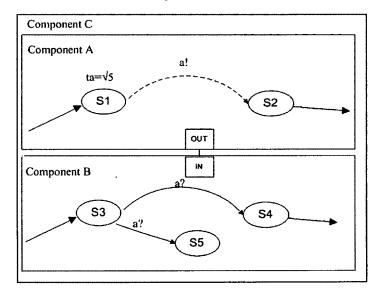

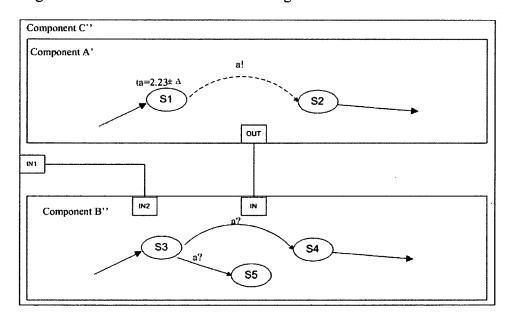

|   | Figure 22: A coupled DEVS model                                                | 90  |

|   | Figure 23: RTA-DEVS component with External Input.                             | 91  |

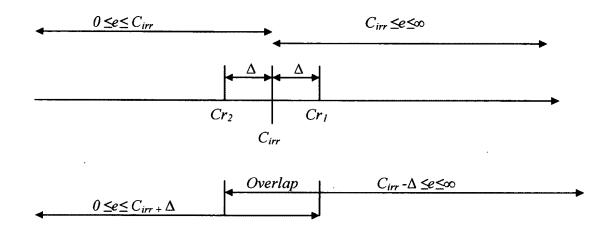

|   | Figure 24: Overlap of two intervals because of approximating irrational value  | 94  |

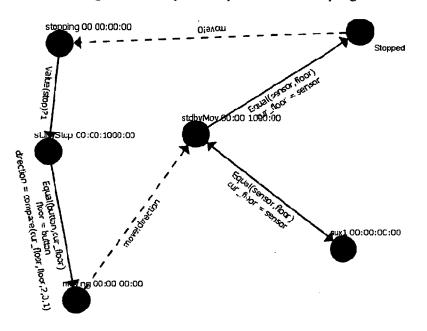

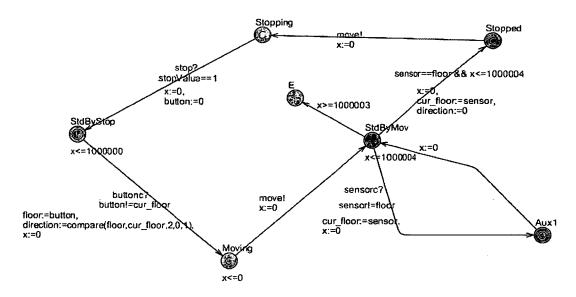

|   | Figure 25: Elevator RTA-DEVS Model.                                            | 96  |

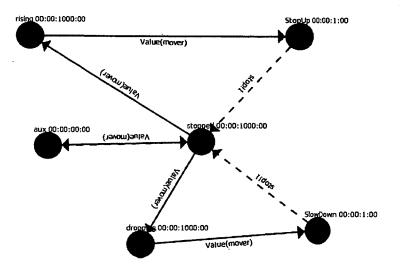

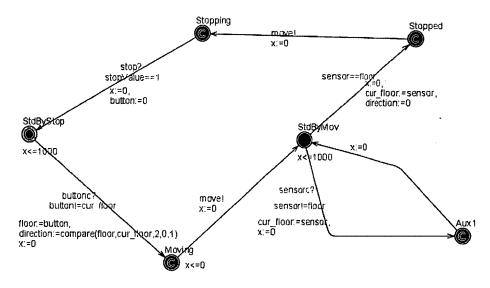

|   | Figure 26: Elevator TA model.                                                  | 97  |

|   | Figure 27: Elevator Controller Model as DEVS Graphs.                           | 98  |

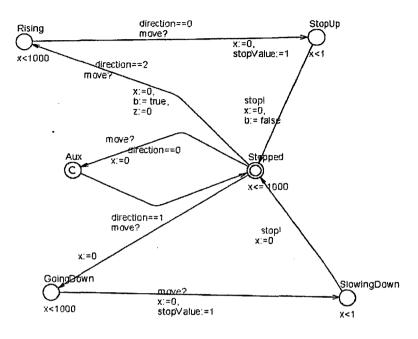

|   | Figure 28: TA Controller model in UPPAAL                                       | 99  |

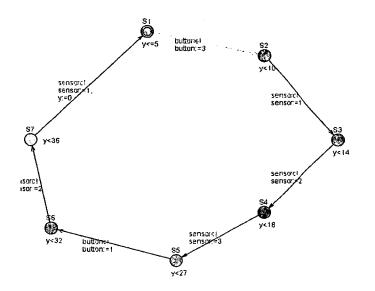

|   | Figure 29: Environment inputs (Button and Sensor) 1                            | 01  |

|   | Figure 30: Elevator Verification Results in UPPAAL 1                           | .02 |

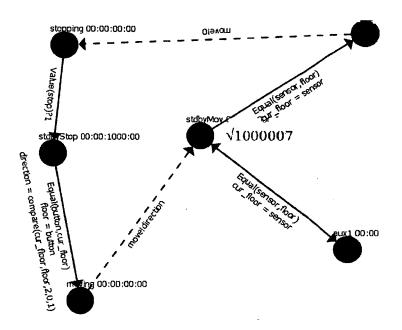

|   | Figure 31: Elevator-Controller in DEVS Graphs notation with irrational value 1 | .04 |

|   | Figure 32: TA Controller model with Non-deterministic behaviour 1              | 05  |

|   | Figure 33: Exact solution for the exponential decay formula 1                  | 09  |

|   | Figure 34: Quantized representation of exponential decay                       | 12  |

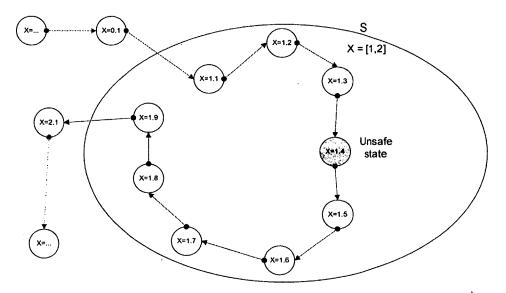

|   | Figure 35: Example of real numbers over-approximation with integer numbers 1   | 16  |

|   | Figure 36: TA model of exponential decay formula                               | 19  |

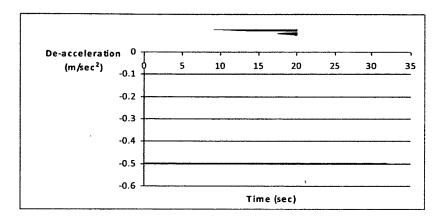

|   | Figure 37: Elevator braking. De-acceleration: 0.5 m/s <sup>2</sup>             | 21  |

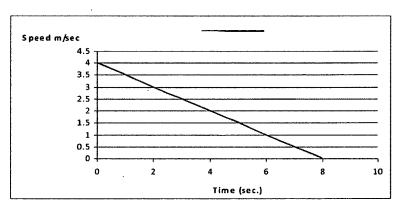

|   | Figure 38: Elevator speed under braking                                        | 121 |

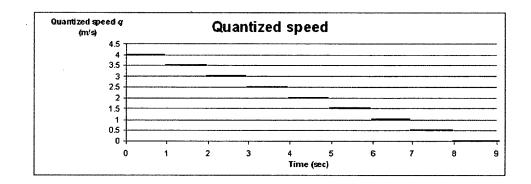

|   | Figure 39: Quantized braking-elevator speed.                                   | 122 |

|   | Figure 40: TA model of braking elevator motion                     | . 123 |

|---|--------------------------------------------------------------------|-------|

|   | Figure 41: Modified elevator TA model- scale of 1/100 second       | . 124 |

|   | Figure 42: Elevator speed, acceleration= - 0.12 m/sec <sup>2</sup> | . 126 |

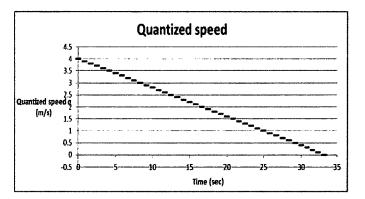

|   | Figure 43: Quantized speed, acceleration= - 0.12 m/s <sup>2</sup>  | . 126 |

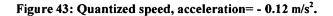

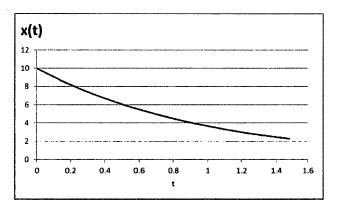

|   | Figure 44: Exact solution for exponential decay formula            | . 129 |

| , | Figure 45: QSS linear approximation                                | . 130 |

|   | Figure 46: Over-approximation of QSS trace                         | . 131 |

|   | Figure 47: Safety zones with QSS over-approximation.               | . 132 |

|   | Figure 48: TA model of a QSS general Integrator                    | . 138 |

|   | Figure 49: TA Model of a QSS Input function generation             | . 140 |

|   | Figure 50: Definition template of $u(t)$ in UPPAAL                 | . 146 |

`

.

. .

### Acronyms

- DEVS Discrete EVent System Specification

- P-DEVS Parallel DEVS

- RT-DEVS Real-Time DEVS

- FD-DEVS Finite and Deterministic DEVS

- SP-DEVS Schedule Preserving DEVS.

- M&S Modeling and Simulation

- RC Root Coordinator

- TA Timed Automata

- E-CD++ Embedded CD++

- IDE Integrated Development Environment

- GGAD Generic Graphical Advanced environment for DEVS modeling and simulation

- RTA-DEVS Rational Time Advance DEVS

- QSS Quantized State Systems method

- STDEVS Stochastic DEVS

- CTL Computation Tree Logic

- PTCTL Probabilistic Timed computation Tree Logic

- RT Real-Time

- RTS Real-Time Systems

## **Chapter 1: Introduction**

Real-Time (RT) systems are advanced computer systems with hardware and software components with timing constraints. In some cases, they have "soft" timing constraints in which a deadline can be missed without serious consequences. In other cases, the system must satisfy "hard" timing constraints, and a missed deadline can result in catastrophic consequences. In these highly reactive systems, not only is correctness critical, but also the timeliness of the executing tasks. Embedded RT software systems are increasingly used in mission critical applications, where a failure of the system to deliver its function can be catastrophic. For instance, if we consider the design decisions made for an aircraft autopilot, or a controller for an automated factory, we need to obtain system responses within well-defined deadlines. Great care must be taken when developing RT systems to guarantee functional correctness along with non-functional correctness such as timing constraints.

Because of the growing complexity of RT systems and their need for high reliability, RT software development is still time-consuming, error-prone, and expensive, requiring a difficult and costly development effort with no guarantee for a bug-free software product. Many techniques have been proposed and used in practice to check correctness of RT software. Current RT engineering methodologies use modeling as a method to study and evaluate different system designs before building the real application. In this way, real systems would have a very high predictability and reliability. In order to apply this methodology, a designer must abstract the physical system at hand and build a model for it, then combine this with a model of the proposed controller design. Then, different techniques can be used to reason about these models and gain confidence in their correctness. Informal methods usually rely on extensive testing of the systems based on system specifications [1]. These methods have limitations because, in order to guarantee software reliability, we need to apply exhaustive testing to the software component, using all possible input combinations, which is a costly process. Many techniques have been proposed to enable a practical alternative to this exhaustive software testing [2]. However, we cannot guarantee a full coverage of all possible execution paths in a software component, thus leaving us with limited confidence in software correctness. Therefore, informal techniques can reveal errors, but they cannot prove the non-existence of errors.

The use of formal software analysis is growing as an alternative, as this technique allows full verification that software components are free of errors. In the last few decades, these techniques have matured and been used in some industrial capacity for software and hardware correctness verification [3]. Formal techniques can be used to prove the correctness of systems specifications. Nevertheless, they are usually constrained in their application, as they do not scale up well. Likewise, the designers need a high level of expertise to apply these techniques. Another drawback of formal techniques is their need to be applied to an abstract model of the real system, which means that what is being verified is not the final implementation. Even if the abstract designed model is proven correct, there is a risk that some errors creep in during the development process through the manual implementation of the design into executable code [1].

Formal verification techniques are of two main types, *deductive* or *algorithmic* [4]. Deductive techniques rely on representing the system and its specification with logic rules, and then trying to deduct a proof of system correctness. In this method, the user needs to find a sequence of deductions to reach the proof; hence, deductive technique needs more creativity and expertise with formal methods from the user than algorithmic one. This becomes a disadvantage with the growing size of systems, as manual intervention, required from the user, also grows. The advantage of this technique, however, is that it can deal with systems of infinite state space, which usually is the case found in hybrid systems. Algorithmic techniques rely on modelling the system in a graphical form, and coding the specifications in logical queries. Then an algorithm for reachability analysis searches the graph space for nodes that satisfy specification queries and are reachable from the initial system configuration. This method is also called model checking. For a system composed of multiple components, the model checking algorithm combines these models to build one graph representing the system overall behaviour that is called a *reachability graph*. By traversing this graph, the model checking algorithm can check the satisfaction of a given query against the given system model. However, for the algorithm to terminate, the reachability graph must be finite, otherwise termination would

3

not be guaranteed, and the model checking problem would be undecidable. The advantage of this method is its complete automation, and the user does not need to be an expert in formal methods. New theoretical advances in model checking allow engineers to guarantee certain properties about the models of such systems using a formal approach. Model checking techniques can be automated to improve the work of the software engineer. Timed Automata (TA) theory [5], in particular, has provided many practical results in this area. However, there is still a gap between a system model that is checked as an abstract entity, and the actual system implementation code to be run on a target platform. More work is still needed to prevent errors from creeping into the final implementation as the programmer translates the requirements captured and modeled in TA into code. TA and other formal methods have showed promising results, but they are still difficult to apply and have limited power when the complexity of the system under development scales up.

A different approach to deal with these issues considers using Modeling and Simulation (M&S) to gain confidence in the model correctness. The use of M&S is not new, and systems engineers have often relied on these methods in order to improve the study of experimental conditions during model definition. The construction of system models and their analysis through simulation reduces both end costs and risks, while enhancing system capabilities and improving the quality of the final products. M&S let users experiment with "virtual" systems, allowing them to explore changes and test dynamic conditions in a risk-free environment. This is a useful approach, especially considering that testing under actual operating conditions may be impractical and, in some cases, impossible. Nevertheless, no practical, automated approach exists to perform the transition between the modeling and the development phases, and this often results in initial models being abandoned, resulting in increased initial costs that project managers try to avoid. Simultaneously, M&S frameworks are not as robust as their formal counterparts.

Using M&S for RT systems enables testing real life scenarios, even for those cases in which real-life testing might be too costly or impossible to achieve [6]. If the models used for M&S were formal, their correctness would also be verifiable, and a designer could see the system evolution and its inner workings even before starting a simulation. Another advantage of executable models is that they can be deployed to the target platform, thus giving the opportunity to use the model not only for simulations, but also as the actual implementation deployed on the target hardware. This avoids any new errors that could appear during the implementation from transformation of the verified models into an implementation, thus guaranteeing a high degree of correctness and reliability.

#### **1.1 Objectives**

Considering the issues in the previous section, RT system designers need a methodology to help them in the modeling and analysis of any complete design of an RT system. It is useful if the same methodology can be used to formally verify a system against its requirements, and also used to simulate individual scenarios. Finally, after complete

5

verification of the correctness of the designed system, the methodology should ensure that the exact verified design could be deployed and executed on the target platform.

The objective of this thesis is to provide such a practical methodology to build and verify RT systems. This methodology uses two main formalisms to model systems specifications. The first one of them is the Discrete Event System Specifications (DEVS) formalism [7], which is based on systems theory. DEVS is the most general discrete event specification, and one can build complex models as a composite of different methods for the various components (Cellular Automata, Petri Nets, Timed Finite State Machines, Modelica, PDEs and other continuous components) that can be then translated into a DEVS representation. These DEVS models can then be simulated using DEVS abstract simulation algorithms. DEVS simplifies building complex models by its hierarchical building of coupled models out of atomic models. DEVS models are directly executable on many DEVS simulators including an RT DEVS kernel such as e-CD++ [8]. However, DEVS simulators lack formal verification capability and this was the motivation to this thesis.

The second formalism used in our methodology is Timed Automata (TA) [5]. The TA formalism, which is based on finite automata theory, was proposed to specify RT reactive systems. TA provides a solid theory and algorithms for model checking, and many existing tools implement these algorithms (for instance, UPPAAL, Kronos and others [9], [10]). TA's main concern is building an abstract formal description of the system that is verifiable by model checking, and is not focused on simulating discrete systems; thus, its

tools lack many functions that usually exist in DEVS simulators and allow simulating different systems.

Given the strengths and weaknesses of these two formalisms, the objective of this thesis is to develop a methodology that combines both formalisms to allow the designer to model, simulate, verify, and deploy RT systems. This is achieved by guaranteeing the correctness of the model with a methodology that verifies DEVS models with TA model-checking techniques and tools. The verified DEVS models would then execute directly on an RT DEVS kernel, thus eliminating the risk of introducing errors in the final system implementation on the target platform. This methodology gives a model-based approach in which the user can move the original verified models to a target platform to execute them in RT without any changes. The resulting systems developed with this methodology would have a higher correctness and reliability of the actual code executing in the RT system. During this research this concept is demonstrated in actual elevator controllers running in real-time scenarios.

#### **1.2 Originality of the Research**

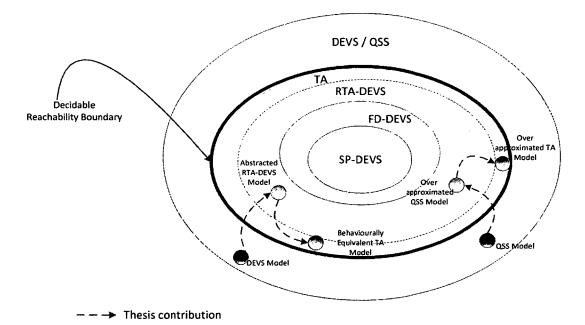

The originality of this research relies in the introduction of a new practical methodology to verify DEVS models. The methodology introduced here differs from other existing approaches in that it targets the verification of classic DEVS models and not a subset of DEVS formalism. This allows the modeller to use the classic full DEVS formalism and makes this methodology a good option to be used in an embedded systems development lifecycle methodology. The verification of DEVS introduced in this thesis is done on multiple stages. First, it defines a new class of DEVS, called **RTA-DEVS**, which is close to classic DEVS in semantics and expressive power. Then, the methodology defines a transformation to obtain a TA that is behaviourally equivalent to RTA-DEVS. The advantage of doing so is that many classic DEVS models would satisfy the semantics of RTA-DEVS models. Thus, they could be simulated with any DEVS simulator. Likewise, it could be transformed to TA to validate the desired properties formally. RTA-DEVS is close to general DEVS, in its expressiveness; nevertheless, as we will show later in the methodology, it is a verifiable subset of DEVS.

The second stage in the verification deals with the approximations and abstractions carried out for transforming DEVS models into RTA-DEVS. To assess their effect on verification accuracy, we propose a method to estimate if any errors were introduced during the transformation that may affect the verification step, or the validity of the resulting RTA-DEVS model.

A new approach is also introduced to build on the above results to enable the formal verification of **hybrid systems** (composed of discrete and continuous components) built with DEVS formalism. All of these research topics are original research ideas that have not been found in the literature of this domain.

#### **1.3 Structure of the Thesis**

This thesis is structured as follows: Chapter 2 provides the reader with a review of the state of the art of literature related to the research. In this chapter, we also introduce the

main concepts used, including an introduction to the DEVS formalism, related work of different approaches used to verify DEVS models, an introduction to Timed Safety Automata, and to the QSS method, which will be used to model continuous systems with discrete DEVS models. We also introduce a summary of this thesis contribution in this chapter.

Chapter 3 presents the proposed RTA-DEVS formalism, and it shows how it is mapped to TA for the purpose of formal verification. An example is introduced to show the proposed methodology and algorithm. We also describe a method to transform DEVS models to RTA-DEVS with the ability to tell if this transformation would cause an effect to verification results.

Chapter 4 discusses the work to verify hybrid systems built with Quantized State Systems method QSS and DEVS components.

In chapter 5, we present the conclusion for this research, and potential future research.

### Chapter 2: Survey of State of the Art

In this chapter, we will introduce a brief state of the art related to our thesis research. This includes a brief introduction to DEVS formalism, coverage of different techniques that have been used in literature for verification and testing of DEVS models, a brief introduction to timed automata theory and formalism, and an introduction to a topic of interest to our methodology that is modeling hybrid systems with a discrete event representation using DEVS components.

These topics would constitute an essential background to understand our methodology and to introduce our thesis in the following chapters.

#### 2.1 Discrete Event System Specification (DEVS).

DEVS [7] is an accepted framework for understanding and supporting the activities of modeling and simulation. DEVS is a sound formal framework based on systems theory. It includes well-defined coupling of components, hierarchical, modular construction, support for discrete event approximation of continuous systems, support for stochastic systems, and enables component reuse. DEVS theory provides a rigorous methodology for representing models, and it does present an abstract way of thinking about the world independent of simulation mechanisms, underlying hardware and middleware. A real system modeled with DEVS is described as a composite of sub-models, each of them being atomic (behavioural) or coupled (structural).

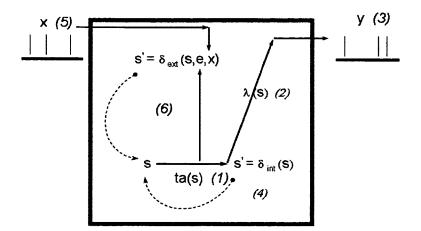

The basic modelling unit of DEVS is called an *atomic* model. A DEVS atomic component is formally defined as:

$$AM = \langle X, S, Y, \delta_{ext}, \delta_{int}, \lambda, ta \rangle$$

(Eq. 2.1)

Where:

X: a set of external input event types

S: a sequential state set

Y: an output set

$\delta_{ext}: Q \times X \rightarrow S$ , an external transition function

Where Q is the total state set of  $M = \{(s, e) | s \in S \text{ and } 0 \le e \le ta(s)\}$

$\delta_{int}: S \rightarrow S$ , an internal transition function

$\lambda: S \to Y$ , an output function

*ta*:  $S \rightarrow \Re^+_{0,\infty}$ , a time advance function

Where the  $\mathfrak{R}^+_{0,\infty}$  is the non-negative real numbers with  $\infty$  adjoined.

An atomic component AM is a model that is affected by external input events X, and it generates output events Y. The state set S represents the unique description of the states of the model. The internal transition function  $\delta_{int}$  and the external transition function  $\delta_{ext}$ compute the next state of the model. If an external event arrives at elapsed time e which is less than or equal to a value specified by the time advance function ta(s), a new state s'is computed by the external transition function  $\delta_{ext}$ . Then, a new ta(s') is computed, and the elapsed time e is set to zero. Otherwise, if no external event arrives before the state lifetime elapses, a new state s' is computed by the internal transition function  $\delta_{int}$ . In the case of an internal event, the output specified by the output function  $\lambda$  is produced based on the state s. As before, a new ta(s') is computed, and the elapsed time e is set to zero.

Figure 1 illustrates the state transition of an atomic component. This diagram describes the behaviour of an atomic model as sequence of steps indicated by the numbers on the diagram. In the first step (1) on the diagram, the atomic component is in state *s* for a specified time ta(s). If the atomic component passes this time without interruption, it will execute its output function  $\lambda(s)$  (step 2) to produce an output *y* (step 3) at the end of this time and will change state based on its  $\delta_{int}$  function (complete transition) to state *s* in step 4, and then this new state becomes the component state and we consider it as state *s* which now is the component state (this is indicated by the dotted arrow from *s* to *s* on the bottom of the diagram). Continuing from this new state *s* (this is state which is determined by its  $\delta_{ext}$  function (step 6) and does not produce an output (incomplete transition). Again we consider this new state the component state *s* (this is indicated by the dotted arrow from *s* to *s* on the left of the diagram) and the component waits in this state for the next event to repeat the previous cycle.

Figure 1: DEVS atomic component state transition sequence (extracted, with permission, from [7]).

A coupled model connects the basic models together in order to form a new model. This model can itself be employed as a component in a larger coupled model, thereby allowing the hierarchical construction of complex models. The coupled model is defined as:

$$N = \langle X, Y, D, \{M_d | d \in D\}, EIC, EOC, IC, SELECT \rangle$$

(Eq. 2.2)

Where:

$X = \{(p, v) | p \in IPorts, v \in X_p\} \text{ is the set of input ports and input values for these ports;}$  $Y = \{(p, v) | p \in OPorts, v \in Y_p\} \text{ is the set of output ports and output values for these ports;}$

D is the set of the component names.

Each component d is a DEVS model, we express each component as d ∈ D with its DEVS atomic model defined as:  $M_d = (X_d, Y_d, S, \delta_{int}, \delta_{ext}, \lambda, ta)$

Where  $X_d = \{(\mathbf{p}, \mathbf{v}) \mid \mathbf{p} \in IPorts_d, \mathbf{v} \in X_P\},\$

$$Y_d = \{(\mathbf{p}, \mathbf{v}) \mid \mathbf{p} \in OPorts_d, \mathbf{v} \in Y_P\}$$

The component couplings are subject to the following requirements:

External input coupling (EIC) connects external inputs of the coupled model to component inputs,

$EIC \subseteq \{((N, ip_N), (d, ip_d)) \mid ip_N \in IPorts, d \in D, ip_d \in IPorts_d\};$

External output coupling (EOC) connects component outputs to external outputs,

$$EOC \subseteq \{((d, op_d), (N, op_N)) \mid op_N \in OPorts, d \in D, op_d \in OPorts_d\};$$

Internal coupling (IC) connects component outputs to component inputs,

$$IC \subseteq \{((a, op_a), (b, ip_b)) \mid a, b \in D, op_a \in OPorts_a, ip_b \in IPorts_b\};\$$

SELECT:  $2^M \rightarrow M$ , the tie-breaking selector

A coupled DEVS model is defined with the restriction that no feedback loop is allowed, i.e. no output port of a component should be connected to one of its input ports.

A coupled model N consists of components  $M_i$  which are atomic components and/or coupled models. The influences  $I_i$  and the *i*-to-*j* output translation  $Z_{i,j}$  define three types of coupling specifications as follows. The external input coupling EIC connects the input events of the coupled model itself to one or more of the input events of its components. The external output coupling EOC connects the output events of the components to the output events of the coupled model itself. The internal coupling IC connects the output events of the components to the input events of other components. In these definitions,  $I_i$  represents set of components that are connected to the input, while  $Z_{i,j}$  represents any connections from an output of a component to the input of another component. The *SELECT* function is used to order the processing of the simultaneous events for sequential events. Thus, all the events with the same time in the system can be ordered with this function.

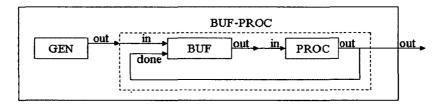

Figure 2 shows a hierarchical DEVS model. This model is composed of two atomic components (Generator, Buffer and Processor) and two coupled models: the top model contains the generator atomic component and the BUF-PROC coupled model, the BUF-PROC coupled model includes two atomic components: BUF and PROC. The port connections are also visible in the figure. For example the output port "out" of atomic component PROC is connected to the "done" input port of the BUF atomic component within the same coupled model and is also connected to the output port.

#### Figure 2: DEVS Model Hierarchy.

DEVS models are executed inside a DEVS *simulator* or *executer*. This simulator loads the DEVS model, reads any external event that may exist, and executes the transition functions defined in the DEVS model. Any output generated from the DEVS

model is produced to the environment from the DEVS simulator. Some examples of DEVS simulators are CD++ [11], PowerDEVS [12], adevs [13] and DEVSJAVA [14].

DEVS simulators are also available to run on embedded platforms allowing DEVS models to run as embedded software in RT. Some initial work on executing DEVS models in real time was done in [15] to execute DEVS models on a chip. More advanced simulators were developed, for example PowerDEVS [16]. PowerDEVS has the ability to execute models on a RT operating system with synchronization of simulation time to RT clock. With its ability to model continuous systems within DEVS, the RT execution of DEVS allows simulation of physical systems in RT.

RTDEVS/CORBA [17] is a RT simulator designed to model and simulate large-scale distributed RT systems. This simulator supports the concept of model continuity that means the same model of a system can be used through all design phases. This simulator provides RT modeling & simulation environment so that the system under study can be simulated with its environment model in real-time. Zeigler in [7] describes the internal architecture of such RT simulator and some differences of RT simulator from the classic DEVS simulator to increase performance and enable interaction with underlying operating system to support concurrent execution threads.

E-CD++ [8] is an embedded DEVS simulator that can execute DEVS models in RT and interacts with external sensor and actuators as shown in a case study in [18]. Using DEVS models as executable models on an embedded platform closes the gap between modeling and implementation, thus avoiding errors that may be introduced by the manual translation of models into executable code. This approach can be greatly enhanced with the ability to validate DEVS models not only through simulation, but also with the ability to formally verify the model against the initial requirements. In this case, DEVS models would be proven free of defects, and its direct execution on embedded platform eliminates any possible creep of defects into the executed code. The goal of this thesis therefore, is to present a robust methodology to formally verify DEVS models using different formal techniques and methods, and giving the system modeller a robust method to estimate the effect of any approximations necessary to achieve that goal.

#### 2.2 Timed Automata (TA)

A Timed Automaton can be defined as in [10]:

$$A = (N, I_0, E, I)$$

(Eq. 2.3)

-N is a finite set of locations (or nodes),

$-l_o \in N$  is the initial location,

$-E \subseteq N \times \beta(C) \times \sum \times 2^C \times N$  is the set of edges and

$-I: N \rightarrow \beta(C)$  assigns invariants to locations

Here, C is a set of clock variables (with x, y,... representing clock variables from the set C). We use a, b, etc. to represent the actions from a set of the finite alphabet  $\Sigma$ . Let us assume a finite set of real-valued variables C ranged over by clocks x, y,... and a finite alphabet  $\Sigma$  (with actions a, b, ...). Let us call a *clock constraint* to a conjunctive formula of atomic constraints of the form  $x \sim n$  or  $x - y \sim n$  where x, y are clock variables,  $\sim$  is one of  $\{\leq, <, =, >, \geq\}$  and n is a natural number. The clock constraints can be used on transitions,

where they are called *guards*; or in a location (state), where they are called *invariants*. Invariants are constraints on the form  $x \le n$ , or x < n to restrict time spent in a TA location.  $\beta(C)$  denotes set of clock constraints. We use the notation u - I(l) to mean that clock valuation u satisfies the invariant defined in location l. We also define a TA state as a pair of (*location, clock valuation*) such as (L, u).

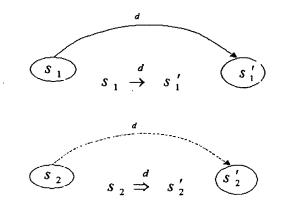

TA are *Timed Transition Specifications* in which the states are pairs  $\langle L, u \rangle$ , where L is a location, and u is a clock valuation. We write  $l \xrightarrow{g,a,r} l'$  when  $(l,g,a,r,l') \in E$  with g a clock constraint, a an action, and r a set of clocks to be reset to zero.

TA uses two types of transitions:

- Delay Transitions:  $\langle L, u \rangle \xrightarrow{d} \langle L, u + d \rangle$ , where the time passage d causes a transition from a start location L to an end location L if u + I(L) and (u+d) + I(L).

- Action transitions:  $\langle L, u \rangle \xrightarrow{a} \langle L', u' \rangle$ , where an action *a* causes a transition from a start location *L*, to an end location *L'*, and  $u' \neq I(L)$ .

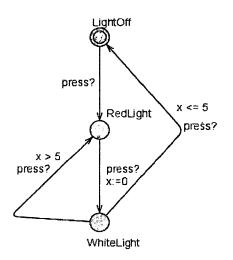

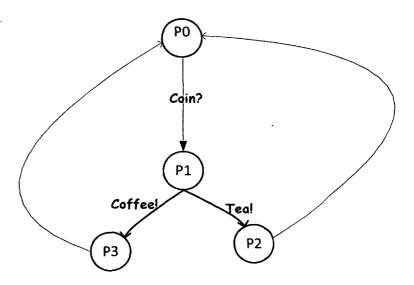

Figure 3: Timed Automaton

An example of a timed automaton is shown in figure 3. This model represents a light that can be either off, operating in red mode, or in white mode. The light changes modes depending on the user pressing the light switch button. From the red mode if the switch is pressed twice within 5 seconds, the light goes to white then to *off*, otherwise it goes to white then back to red. In order to do that, the TA uses three states. *LightOff* is the initial state, which represents that the light is turned off. The transition out of *WhiteLight* to *LightOff* has the a guard  $x \le 5$  which enables the transition only while clock x value stays less than 5 time units, whenever a synchronization signal arrives on channel *press*. States could also have clock constraints and in this case, they are called *invariants*. In this case, time is allowed to pass in a state while the clock values satisfy the invariant. Once the invariant is not satisfied, the automaton would leave that state and enable a transition to another state, in which current clock values would satisfy that state invariant. TA is suitable for modeling discrete systems with continuous time. These systems could be

composed of a single TA model, or multiple models that interact together. The latter case is called a *network* of TA.

#### 2.2.1 TA and Model Checking

One of the most successful techniques for systems formal verification is *model checking* [19]. In this method, the system to be verified is modeled by a suitable formalism such as I/O automata or TA, which can be represented in a graphical notation. Each state of the model assumes some valid system property(ies) at this state.

System requirements are specified as a temporal logic formula called *query*. The model checking technique then uses an *algorithmic* approach to *traverse* the model graph, and it checks the satisfaction of the query against the properties defined at each state. For a system composed of multiple components, the model checking algorithm combines these models to build one graph representing the system overall behaviour that is called a *reachability graph*. By traversing this graph, the model checking algorithm can check the satisfaction of a given query against the given system model. However, for the algorithm to terminate, the reachability graph must be finite, otherwise termination would not be guaranteed, and the model checking problem would be undecidable. With timed formalisms such as TA, the time elapse is modeled by a continuous clock variable. This variable value increases when TA is waiting in a state. Even for a bounded Real interval, the number of Real values would be infinite as shown by the famous Cantor's diagonal method. However, TA model checking for finite state machines [20][21][22] was enabled by extending symbolic model checking techniques [23][24] to build a finite reachability

graph with continuous time. Nevertheless, the *state explosion* problem still limits the size of actual problems that can be solved. The state explosion problem is a term describing the exponential growth of the reachability graph size with the growing number of components and states of each component in a network of TA. This renders the techniques of model checking practically limited to small and medium industrial problems unless combined with other techniques to overcome this exponential growth of the reachability graph.

Recent techniques to reduce this problem have been proposed and these results were implemented in a number of tools for TA model checking with a success to check models of increasing sizes. One of these tools is UPPAAL [9][10] that have extended TA with integer variables, urgent channels and user-defined functions. These extensions increase the conciseness of the model, but not the expressiveness power as shown in [25]. UPPAAL uses a subset of TCTL (Timed Computation Tree Logic) [24] to specify queries for properties in the TA model.

*Timed safety Automata* is the version of TA used in the UPPAAL model checker [10]. This thesis used this class of TA as it suffices for the verification purpose to represent DEVS models and it is verifiable within UPPAAL tool.

In the methodology introduced in this thesis, if UPPAAL (or any other model checker) faces a problem of state explosion, and no answers can be obtained in finite time, the user can use model checking on a rough abstract of the system. From this step, some requirements may not be satisfied in the rough abstract model. These would generate a

trace that can be used as a seed input to a simulated mode to test the models using DEVS simulation. Subcomponents can be verified using TA model checkers, improving the overall quality of the system.

#### 2.3 Related work on DEVS verification techniques.

There have been several proposals to verify DEVS models, ranging from formal modelchecking of restricted classes of DEVS, the generation of traces from DEVS models for testing, the specification of high-level system requirements in TA (and verifying DEVS model against those requirements), or introducing clock constructs to DEVS to conform with TA. In this section, we give an overview of these techniques and compare different approaches. From this comparison, we show how the methodology introduced in chapter 3 closes an existing gap in current techniques.

In [26], Wainer et al. presented the verification of DEVS models, checking the consistency of model structure, the correct coupling of components, and the correct definition of the transition functions. These checks were done statically before executing the models and introduced a component to monitor execution for some verification. However, this approach has a limited ability, as it needs to simulate all possible executions of a model to verify all interactions with the model.

In [27], Hernandez and Giambiasi showed that verification of general DEVS models through reachability analysis is undecidable. They based their deduction on building a DEVS model that simulates a Turing machine. Since the halting problem for Turing machines is undecidable (i.e. with only static analysis, we cannot know if a Turing machine would be in a halting state after execution), Hernandez and Giambiasi concluded that this is also true for DEVS models. Therefore, if we start from an initial state in the DEVS model, we cannot know if we would reach a particular state, and hence reachability analysis for general DEVS is impossible. However, reachability analysis would be possible only for restricted classes of DEVS with finite state space, as the undecidability result was obtained by introducing state variables into DEVS formalism with infinite number of values.

Because of the above undecidability result, many approaches have created restricted DEVS subclasses that are verifiable, and in some cases extend original DEVS definition with specific properties for RT systems.

One of these approaches is the *Real-Time DEVS* formalism (RT-DEVS) [28] that extends classic DEVS definition by introducing a time advance function that maps each state to a time-range with maximum and minimum time values. In [29], RT-DEVS was used to model a RT system of train-gate-controller. Song and Kim introduced an algorithm to build a timed reachability tree to check model safety analysis. This work however did not focus on restricting infinite state-space of DEVS for reachability analysis decidability, and it assumed practical RT-DEVS models simulated with modern computers to be an approximation of general DEVS that enables decidable reachability analysis.

In another approach, Hwang defined a subclass of DEVS to enable verification analysis of its models. This was called *Schedule-Preserving DEVS* (SP-DEVS) [30][31][32][33]. SP-DEVS puts the following restrictions on DEVS to obtain finite reachability graph and thus a decidable reachability analysis:

- The sets of states, input, and output events are finite.

- The lifespan of a state can only be a rational number or an infinite time value.

- Preserving the internal transition function schedule after taking any external transition, i.e. if a state transition is caused by an input event, the lifespan and elapsed time are preserved after moving to the new state [33].

These restrictions limited the expressiveness of SP-DEVS to be less than that of classic DEVS; in particular, the last restriction above. Moreover, this restriction caused a problem known as OPNA (Once an SP-DEVS model becomes Passive, it Never returns to become Active), as shown in [30]. This problem results from the restriction of preserving the schedule of the internal transition. Hence, if that schedule was infinity, any subsequent external event will not be able to change it; thus, any passive state can never be interrupted (by the means of assigning a finite time advance value to it).

To solve these issues with SP-DEVS, another sub-class of DEVS was introduced, called *Finite-Deterministic DEVS* (FD-DEVS) [34]. In this work, Hwang mapped the time advance function states only to rational numbers, and prohibited the external transition function to use the elapsed time to compute its result. It also removed the previous restriction of SP-DEVS of preserving the internal schedule, thus avoiding the OPNA problem. With the other restrictions, reachability analysis of FD-DEVS became decidable. Hwang in [34] also introduced an algorithm for verification through

reachability analysis similar to the algorithms and techniques used for TA. However, the restrictions introduced in FD-DEVS for the definition of its external function restricted the expressiveness of FD-DEVS to be much less than classic DEVS. The reachability analysis algorithm introduced for FD-DEVS uses similar techniques as TA, while Hwang and Zeigler in [34] have not claimed an advantage over TA reachability algorithms and tools in time and space complexity. Thus, this approach lacks the support of robust TA model checking tools like UPPAAL or KRONOS, without gaining a tangible advantage.

Another approach for verifying another class of DEVS which is RT-DEVS, is done using TA and UPPAAL. Using this approach, Furfaro and Nigro[35][36] and Cicirelli and Furfaro [37] introduced a transformation from RT-DEVS to UPPAAL. This transformation allows Weak synchronization between components of TA model as RT-DEVS semantics uses Weak synchronization. Once the transformation is done, one obtains a TA model that can be verified with available tools for TA model checking. However, the transformation given did not formally show an equivalence of timed behaviour between RT-DEVS and TA models, and did not introduce a mechanism to approximate irrational values that may be defined in RT-DEVS models, or how to evaluate the impact of such approximation on verification results.

The work presented in [38] by Han and Huang used a different approach to verification of classic parallel DEVS models, based on a method to map DEVS models to TA. However, this was different from the previous approaches, as in this approach, the conversion method mapped both DEVS model and also a representation of the DEVS simulator to TA. The approach suggests trace equivalence as the basis for parallel DEVS and TA model equivalence. This approach considers not only the DEVS model, but also the execution engine semantics and structure to be part of the transformation to TA. As Zeigler et al. shown in [7], in a DEVS simulator, every atomic component has a coordinator component responsible for routing messages from and into the atomic component. Hence, in the verification approach of [38], each atomic model translated to a TA would also need a model of its coordinator translated to TA. Thus, a coupled model composed of *n* atomic DEVS components translated to TA by this approach would also need at least n+1 local coordinators interacting with the global coordinator of the simulator. As each introduced coordinator contains few states and transitions to model its behaviour, the introduction of these n+1 coordinators increases the total number of states in the resultant TA model exponentially, and this adds to the state-space explosion problem. This would limit the practical size of any problem that can be verified by this approach. Another drawback is the notion of trace equivalence between Timed Transition Systems (TTS) as shown by Aceto et al. in [39]. This equivalence is less suitable for reactive systems as it may not reveal subtle errors in the models that would not be observed externally. This was shown in [39] by Aceto et al., as well it was shown that only bi-simulation equivalence can reveal such errors. Also Timed Computational Tree Logic TCTL, which is used to model queries in timed model checking tools such as UPPAAL and Kronos, is not preserved by trace equivalence. This means TCTL queries that are satisfied on TA model may not be satisfied on the original DEVS model.

Dacharry and Giambiasi [40] introduced a similar approach based on TA to verify subclasses of DEVS formalism. They introduced a new class of DEVS called *Time Constrained DEVS* (TC-DEVS), which expanded the DEVS atomic model definition with multiple clocks incremented independently. Classic DEVS atomic models can be seen as having only one clock that keeps track of elapsed time in a state, and is reset on each transition. TC-DEVS also added clock constraints similar to TA (functioning as guards on external and internal transitions). However, it expands on TA guards by allowing clock constraints as state invariants to contain clock differences. TC-DEVS is then transformed to an UPPAAL TA model. However, there is no restriction on the constant values defined in TC-DEVS to be rational numbers. Hence, the resulting TA model from transformation of general TC-DEVS formalism may have undecidable reachability.

Other than proposing verifiable subclasses of DEVS, some other approaches used TA to model high-level system requirements while using the DEVS formalism to model lower-level system design. Then these approaches would build a refinement relation between a DEVS model and a TA model. This approach was followed by Giambiasi et al. in [41]. System requirements are then verified through the simulation of the DEVS model. This approach differs from others in that it does not use formal methods to verify DEVS or TA models, but relies on exhaustive testing through simulation of scenarios. The problem with this is that it is very difficult to cover all scenarios for a system, and it is a resource-intensive exercise to cover even a portion of these scenarios.

Other approaches use semi-formal DEVS verification techniques. Hong and Kim [42] and Labiche and Wainer [43] proposed to analyze the DEVS model formally, and then to generate test scenarios that can be used to verify the DEVS models. These testing scenarios or sequences are generated from model specifications and then applied against the model implementation to verify the conformance of implementation to specifications. A summary of these approaches along with this thesis approach is shown in table 1.

| Verification  | Modelling     | Ability to Ve | rify       | ····     | Coverage of   | Coverage of  | Disadvantages     |

|---------------|---------------|---------------|------------|----------|---------------|--------------|-------------------|

| Method        | Formalism     |               |            |          | classic DEVS  | Hybrid       |                   |

|               |               | Safety        | Bounded    | Deadlock | Verification  | DEVS         |                   |

|               |               |               | Liveness   | Freedom  |               | Models       |                   |

|               |               |               |            |          |               | Verification |                   |

| Static checks | DEVS          | NO (No        | NO (No     | No       | No            | No           | Runtime           |

| and runtime   |               | exhaustive    | exhaustive |          |               |              | monitoring        |

| monitoring    |               | checking)     | checking)  |          |               |              | cannot            |

| [17]          |               |               |            |          |               |              | exhaustively      |

|               |               |               |            |          |               |              | ,<br>check all    |

|               |               |               |            |          |               |              | scenarios.        |

| Reachability  | RT-DEVS       | Yes           | Yes        | Yes      | No treatment  | No           | No Tool support   |

| tree          |               |               |            |          | of irrational |              |                   |

| construction  |               |               |            |          | values.       |              |                   |

| Reachability  | SP-DEVS       | Yes           | Yes        | yes      | No            | No           | No Tool Support   |

| tree          |               |               |            |          |               |              |                   |

| construction  |               |               |            |          |               |              |                   |

| Reachability  | Finite-       | Yes           | Yes        | yes      | No            | No           | lacks the support |

| tree          | Deterministic |               |            |          |               |              | of robust TA      |

| construction  | DEVS (FD-     |               |            |          |               |              | model checking    |

|               | DEVS)         |               |            |          |               |              | tools like        |

Table 1: Related Work of DEVS Verification and Contribution

|            |                  |               |     |     |               |     | UPPAAL or         |

|------------|------------------|---------------|-----|-----|---------------|-----|-------------------|

|            |                  |               |     |     |               |     | KRONOS            |

| UPPAAL TA  | RT-DEVS          | Yes           | Yes | yes | No treatment  | No  | No Proof of       |

|            |                  |               |     |     | of irrational | -   | behavioral        |

|            |                  |               |     |     | values.       |     | equivalence.      |

| TA .       | classic parallel | Yes           | Yes | yes | No treatment  | No  | Used trace        |

|            | DEVS [46]        |               |     |     | of irrational |     | equivalence       |

|            |                  |               |     |     | values.       |     | notion which is   |

|            |                  |               |     |     |               |     | weaker than       |

|            |                  |               |     |     |               |     | bisimulation      |

|            |                  |               |     |     |               |     | equivalence.      |

|            |                  |               |     |     |               |     | Modeled           |

|            |                  |               |     |     |               |     | execution engine  |

|            |                  |               |     |     |               |     | along with the    |

|            |                  |               |     |     |               | •   | system model      |

|            |                  |               |     |     |               |     | which increases   |

|            |                  |               |     |     |               |     | state-space       |

|            |                  |               |     |     |               |     | growth and        |

|            |                  |               |     |     |               |     | verification      |

|            |                  |               |     |     |               |     | complexity.       |

| UPPAAL TA  | Time             | Yes           | Yes | yes | No            | No  | No                |

|            | Constrained      |               |     |     |               |     | transformation    |

|            | DEVS (TC-        |               |     |     |               |     | from DEVS to      |

|            | DEVS)[49]        |               |     |     |               |     | TC-DEVS.          |

| Test cases | DEVS[50]         | Yes           | No  | No  | No            | No  | Cannot work on    |

| generation |                  | (partially),  |     |     |               |     | abstracted DEVS   |

|            |                  | as it is very |     |     |               |     | model to reduce   |

|            |                  | costiy        |     |     |               |     | the problem size. |

| UPPAAL TA  | RTA-DEVS         | Yes           | Yes | Yes | Yes           | Yes |                   |

|            | (This thesis)    |               |     |     |               |     |                   |

.

The techniques we showed so far concern the verification of *hard* real-time systems. In these systems, we cannot tolerate any response missing its deadline. However many real-time systems can tolerate some occasional missing of deadlines, and in this case, the system can still perform its function with some degraded performance. These system are called *soft* real-time. In these systems, a verification question would be "with probability 0.99 or better, the system would respond within 10 time units". Answering this question requires modeling the system in a formalism that allows probabilistic behaviour such as stochastic DEVS [44] and Probabilistic Timed Automata [45].

### 2.4 Hybrid DEVS models

Hybrid models are particularly important in modeling digital control systems where the controlled environment obeys the laws of physics, while the controller can be a digital discrete system or a combination of both digital and analog. The study of such systems requires the verification of the resulting hybrid system.

A major problem in verification of hybrid systems is the lack of a unified theory to model and solve both continuous and discrete components together [46]. As a result, modeling and simulation is still one of the most useful methods to verify this kind of systems [47] [48] [49]. Hybrid systems simulation was enabled within the DEVS formalism by using a new method, called Quantizes State System (QSS) that will be covered in section 2.4.1, which allows modeling continuous components [50][51][52]. However, simulation does not guarantee the absence of defects from the system under study. Simulation verifies the system for particular scenarios chosen by the system tester. As many hybrid systems are embedded in nature, and their failure could cause catastrophic results, it is of most importance to verify these systems for their adherence to requirements and their absence from defects. Formal methods can be used to provide such a guarantee. In doing so, a hybrid system needs to be modeled and verified within a formal framework.

In order to use this algorithmic method (model checking through reachability analysis) to verify hybrid systems, the focus would be to find a suitable finite abstraction of the hybrid system that could be verified, and hence the reachability algorithm could be guaranteed to terminate. Different types of labelled transition systems were proposed to model hybrid systems abstractions including Petri Nets [53], hybrid automata [54] and TA [4].

Some research has used hybrid TA for modeling hybrid systems and verifying them. This type of automata describes the system with a Timed Labelled Transition System (TLTS) and linear differential equations [54]. However, as Henzinger et al. shows in [55], Hybrid TA verification through reachability analysis is not decidable in general. For this reason, recent research has concentrated on modeling the hybrid system in some form with a decidable verification such as TA. In doing so, a technique must be used to model the continuous component in a discrete finite form. As continuous system variables are real values and dense in time (i.e. time scale is continuous and we have infinitely many time points in any bounded interval), their state space could be infinite. An approximation to a finite representation is needed to enable the decidability and termination of reachability analysis. Many techniques have been proposed to approximate the continuous-time systems into a discrete representation of TA [56] [57][58][59].

Although DEVS is a discrete-event system specification, some work has been done to represent continuous systems in a discrete format that can be modeled and simulated with DEVS. One of these methods is Quantized State Systems (QSS) method [51]. Using QSS enables modeling and simulation of hybrid systems with DEVS formalism.

### 2.4.1 The Quantized State Systems (QSS) method

This section is devoted to give a general introduction to the QSS method, as introduced in [50] and [51]. The QSS is an approximation method to model and simulate continuous systems, which are usually modeled with Ordinary Differential Equations (ODE) and Algebraic Equations. This combination of equations describing the system behaviour is generally called Differential Algebraic Equations (DAE). Obtaining a detailed description of the system behaviour entails solving these equations simultaneously. In doing so, many different techniques of numerical integration have been proposed to solve ODEs; namely Euler, Runge-Kutta, etc [60]. These methods approximate the solution of ODEs, and they limit the error to an acceptable range based on the choice of its discrete integration step. All these methods rely on discrete-time integration of ODEs. In this way, time is allowed to progress in small steps, and at each step, an approximation is computed for the ODEs solution. When a system modeled by DAE has a discontinuity (i.e. a sudden jump in its variables values with regard to time), the numerical integration method may

32

produce unacceptable errors [52]. Unfortunately, this kind of discontinuity are normal properties of hybrid systems, which can be seen as operating in different modes, each described with a specific ODEs. An example of such a system would be a heating system with an on-off thermostat switch; in this system, the ODEs describing the system in the heating state (i.e., when the thermostat is in *on* position) are different from those describing cooling state (i.e., the thermostat is in the *off* position).

The Quantized State Systems QSS [50][51][60] is a different method for approximation, a quantization-based method that models hybrid systems as discrete-event systems and not as discrete-time. In the quantization-based method, instead of fixing a time step and calculating the value of the state variable at the next time step, we calculate *when* the state variable reaches a certain value. This value is called a *quantization level*, and the difference between two quantization levels is called the *quantum*. Obviously with a quantization-based method, the time it takes for a state variable to reach a quantization level depends on the state variable slope. The greater the slope, the less time it takes to reach the next level. This produces a variable time-step integration, which becomes an advantage when the system has a vector of state variables, in which each variable has a different change rate (slope). In this case, a variable with large slope would generate more events per unit time, than a variable with a flat slope. As DEVS is an event-based formalism, meaning it would only react to generated or received events, thus a slowchanging variable would need less computations, than a rapidly-changing variable. This event-based property of DEVS also solves the above problem around discontinuities found while solving hybrid systems. In fixed time-step integration methods, the step boundary has to exactly match the point in time in which the discontinuity (or a system jump) happens. Otherwise, the integration would suffer major error if it assumes a continuous trajectory around the discontinuity and handles this in single time step. This problem however, disappears with discrete-event system simulation such as DEVS because whenever an event triggers a discontinuous transition in the system state, DEVS simulator would react to this event and calculate the system state resulting from that event as discussed in [51]. Thus, the integration slope (which is a part of the system state) before the event would be different from that after the discontinuity event. This would guarantee the correct calculation of the system variables before and after the system jump. Consider a continuous system modeled by a time-invariant Ordinary Differential Equation (ODE), and its State Equation System (SES) representation:

$$x'(t) = f[x(t), u(t))]$$

(Eq. 2.4)

Here  $x(t) \in \Re^n$  represents the system state vector such as  $(x_1(t), x_2(t), x_3(t), ..., x_n(t))$  and  $u(t) \in \Re^n$  represents an input vector, which is a known piecewise constant function. With the QSS method, we simulate an approximate system, which is called the Quantized State System:

$$x^{*}(t) = f[q(t), u(t)]$$

(Eq. 2.5)

Where q(t) is a vector of quantized variables  $(q_1(t), q_2(t), ..., q_n(t))$  that are obtained with the quantization function q from the state variables x(t). Each component of q(t) is related to the corresponding component of x(t) by a hysteretic quantization function, which is defined here as given in [51]:

**"Definition 1.** Let  $Q = \{Q_0, Q_1, ..., Q_r\}$  be a set of real numbers where  $Q_{k-1} < Q_k$  with  $1 \le k \le r$ . Let  $\Omega$  be the set of piecewise continuous real valued trajectories and let  $x_i \in \Omega$  be a continuous trajectory. Let  $b: \Omega \to \Omega$  be a mapping and let  $q_i = b(x_i)$  where the trajectory  $q_i$  satisfies:

$$q_{i}(t) = \begin{cases} Q_{m} & \text{if } t = t_{0} \\ Q_{k+1} & \text{if } x_{i}(t) = Q_{k+1} \land q_{i}(t^{-}) = Q_{k} \land k < r \\ Q_{k-1} & \text{if } x_{i}(t) = Q_{k} - \varepsilon \land q_{i}(t^{-}) = Q_{k} \land k > 0 \\ q_{i}(t^{-}) & otherwise \end{cases}$$

Where:

- $Q_m$ : is the initial quantization value at start of time  $t_0$ .

- $Q_{k+1}$ : is the next quantization level at time t if the function slope is positive and last quantization level the function has crossed was  $Q_k$ .

- Q<sub>k-1</sub>: is the next quantization level at time t if the function slope is negative, the last quantization level the function crossed was Q<sub>k</sub>, and the function value x<sub>i</sub>(t) is less than quantization level Q<sub>k</sub> by the hysteresis value ε.

- t is a point in time such that t < t

The index *m* is described by:

$$m = \begin{cases} 0 & \text{if } x_i(t_0) < Q_0 \\ r & \text{if } x_i(t_0) \ge Q_r \\ j & \text{if } Q_j \le x_i(t_0) < Q_{j+1} \end{cases}$$

Then, the map b is a hysteretic quantization function.

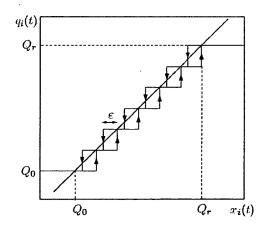

The discrete values  $Q_k$  are called *quantization levels* and the distance between two successive quantization levels  $(Q_{k+1} - Q_k)$  is defined as the *quantum*, which is usually constant. The width of the hysteresis window is  $\varepsilon$ . The values  $Q_0$  and  $Q_r$  are the lower and upper saturation bounds. Figure 4 shows a typical quantization function with uniform quantization intervals." [51]

As shown in figure 4, a hysteresis function approximates a continuous linear function  $x_i(t)$  by outputting a number of discrete levels. The crossing of the continuous function to a quantization level generates an output. Notice however that the output value chosen of  $x_i(t)$  differs when the continuous function  $x_i(t)$  increases from that when the function decreases. This difference or *delay* is the hysteresis window  $\varepsilon$ . Hence an output is dependent not only on the value of the function  $x_i(t)$ , but also on the history preceding this value. The use of hysteresis function is typically to prevent rapid switching of output if value of  $x_i(t)$  fluctuates around some quantization level  $Q_i$ .

Figure 4: Quantization Function with Hysteresis (extracted, with permission, from [51]).

A DEVS model that solves (Eq. 2.5) by integration is called a *quantized integrator* and can be written as follows [51]:

$$M_1 = (X, Y, S, \delta_{int}, \delta_{ext}, \lambda, ta), \text{ where:}$$

(Eq. 2.6)

$X = \Re \times \{\text{inport}\}$

$Y = \Re \times \{\text{outport}\}$

$S = \Re^2 \times Z \times R_0^+ \infty$

$\delta_{int}(s) = \delta_{int}(x, d_x, k, \sigma) = (x + \sigma \cdot d_x, d_x, k + sgn(d_x), \sigma_1)$

$\delta_{\text{ext}}(s, e, x_{\nu}) = \delta_{\text{ext}}(x, d_x, k, \sigma, e, x_{\nu}, \text{port}) = (x + e \cdot d_x, x_{\nu}, k, \sigma_2)$

$\lambda(s) = \lambda(x, d_x, k, \sigma) = (Q_{k + \text{sgn}(d_k)}, \text{ outport})$

$ta(s) = ta(x, d_x, k, \sigma) = \sigma$

Where :

$R_0^+ \infty$ : Are the positive real numbers

{Inport}: Set of Input ports.

{Outport}: Set of Output ports.

$$\sigma_{1} = \begin{cases} \frac{Q_{k+2} - (Q_{k+1})}{d_{x}} & \text{if } d_{x} > 0\\ \frac{Q_{k} - (Q_{k-1} - \varepsilon)}{|d_{x}|} & \text{if } d_{x} < 0\\ \infty & \text{if } d_{x} = 0 \end{cases} \text{ and }$$

$$\sigma_{2} = \begin{cases} \frac{Q_{k+1} - (x + e.d_{x})}{x_{v}} & \text{if } x_{v} > 0\\ \frac{(x + e.d_{x}) - (Q_{k} - \varepsilon)}{|x_{v}|} & \text{if } x_{v} < 0\\ \infty & \text{if } x_{v} = 0 \end{cases}$$

A static function  $f(z_1, \ldots, z_p)$  can be represented by the DEVS model:

$$M_2 = (X, Y, S, \delta_{int}, \delta_{ext}, \lambda, ta), \text{ where}$$

(Eq. 2.7)

$X = \Re \times \{\text{inport}_{1}, \dots, \text{inport}_{p}\}$   $Y = \Re \times \{\text{outport}\}$   $S = \Re^{p} \times \Re^{+}_{0} \infty$   $\delta_{int}(s) = \delta_{int}(z_{1}, \dots, z_{p}, \sigma) = (z_{1}, \dots, z_{p}, \infty)$   $\delta_{ext}(s, e, x) = \delta_{ext}(z_{1}, \dots, z_{p}, \sigma, e, x_{v}, port) =$   $(z_{1}, \dots, z_{p}, \infty)$   $\lambda(s) = \lambda(z_{1}, \dots, z_{p}, \sigma) = (f(z_{1}, \dots, z_{p}, \sigma), outport)$

$ta(s) = ta(z_1, \ldots, z_p, \sigma) = \sigma$

Where

$$\widetilde{z} = \begin{cases} x_v & \text{if port = inport}_j \\ z_j & \text{otherwise} \end{cases}$$

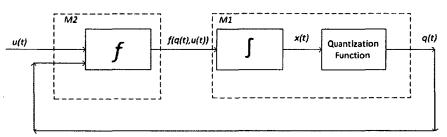

As indicated in [51], this combined DEVS model of  $M_1$  and  $M_2$  simulates the QSS system.

Figure 5 shows a DEVS coupled model for a QSS model as defined by (Eq. 2.6) and (Eq. 2.7). The Model M<sub>1</sub> defines the integrator and the quantization function. This model has an input set X which contains pairs of (*Real number, inport number*), an output set Y that contains pairs (*Real number, outport number*), and a set of system states S that represents different states which the QSS system would have. Each state is represented with a tuple of the form  $(x, d_x, k, \sigma)$  where x is the state variable value,  $d_x$  is the state variable rate of change (slope), k is the index of the current quantization level  $Q_k$ , and  $\sigma$  is the state lifetime.

Figure 5: QSS Block Diagram Model

The behaviour of model  $M_1$  is determined by its transition functions  $\delta_{int}(s)$  and  $\delta_{ext}(s, e, x)$ . The function  $\delta_{int}(s)$  defines the internal transition function. This function transfers the system from its current state to a target state, and is executed when the state lifetime has elapsed. The target state of this function is always the next quantization level, which is expressed as the integration  $x + \sigma d_x = Q_{k+sign}(dx) = Q_{k+1}$  (in case of a positive slope  $d_x$ ).

The lifetime of this target state  $\sigma_1$  is the time needed to reach the next quantization level  $Q_{k+2}$  and is calculated as shown above in (Eq. 2.6).  $\delta_{ext}(s, e, x)$  defines the external transition function, and it is triggered whenever an input reaches an *inport*. In this model, the input is a pair ( $x_{v}$ , port) where  $x_v$  is the slope calculated as  $x_v = f(q(t), u(t))$ , as shown in the diagram of Figure 5. The target state of this function is a new state with an updated value of the state variable  $x_{i+1} = x_i + e.d_x$ , new slope  $x_v$ , and a new calculated lifetime  $\sigma_2$  equals to the time needed to reach the next quantization level.  $\lambda(s)$  in M<sub>1</sub> is the output function and when triggered, it sends the value of the current quantization level to the outport. M<sub>2</sub> models a static function that accepts q(t) and u(t) as inputs and calculates f(q(t), u(t)).

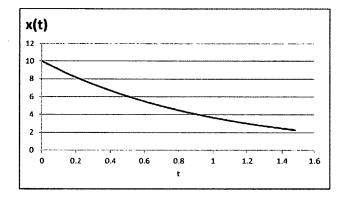

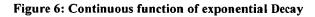

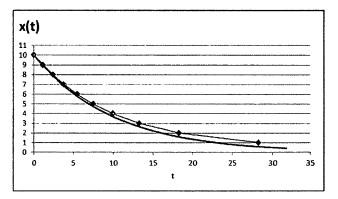

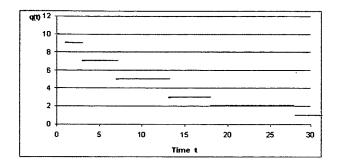

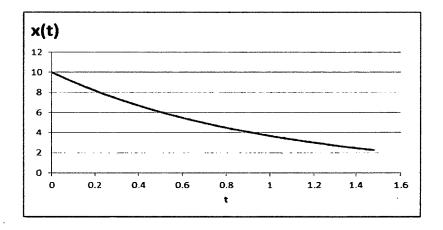

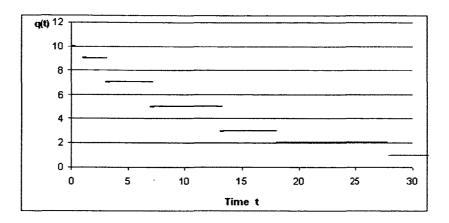

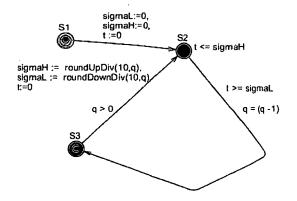

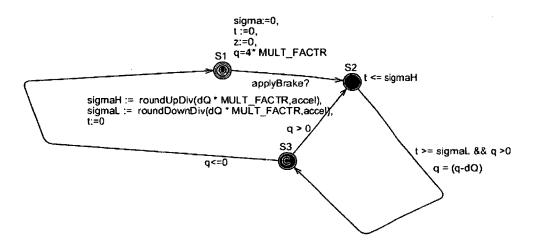

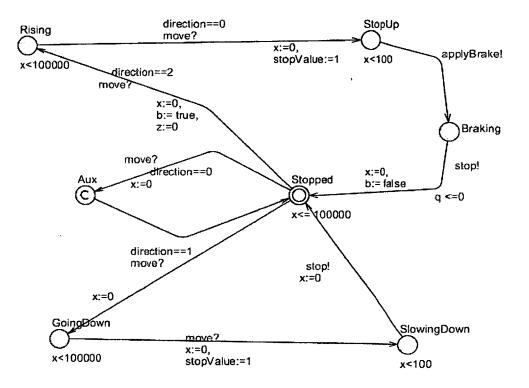

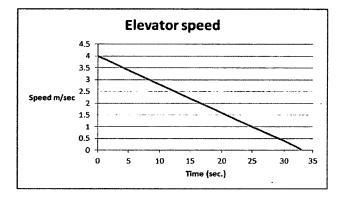

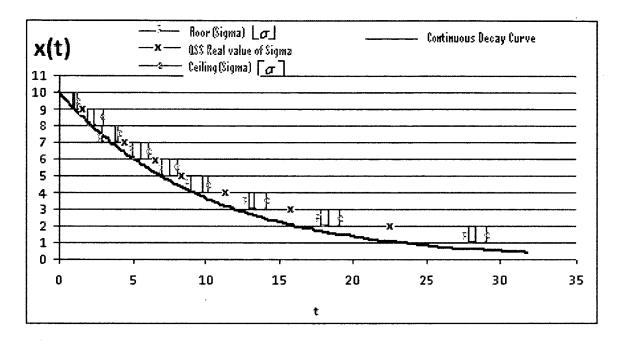

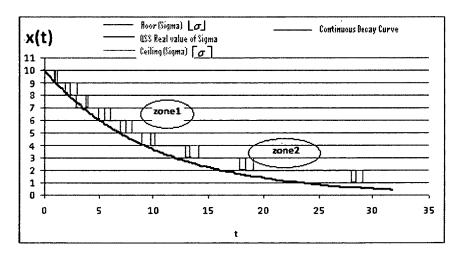

An example of the quantization of an exponential decay function is shown below. The continuous representation of the function is shown in figure 6, its linear approximation as defined by the QSS method is shown in figure 7, while its quantized representation is shown in figure 8.