# Bare-Metal Kernels for DEVS Model Execution in Embedded Systems

by

#### Daniella Niyonkuru, B.Eng.

A thesis submitted to the Faculty of Graduate and Postdoctoral Affairs in partial fulfillment of the requirements for the degree of

#### Master of Applied Science in Electrical and Computer Engineering

Ottawa-Carleton Institute for Electrical and Computer Engineering

Department of Systems and Computer Engineering

Carleton University

Ottawa, Ontario

August, 2015

©Copyright

Daniella Niyonkuru, 2015

The undersigned hereby recommends to the Faculty of Graduate and Postdoctoral Affairs acceptance of the thesis

# Bare-Metal Kernels for DEVS Model Execution in Embedded Systems

submitted by Daniella Niyonkuru, B.Eng.

in partial fulfillment of the requirements for the degree of

Master of Applied Science in Electrical and Computer Engineering

| Professor Gabriel Wainer, Thesis Supervisor    |

|------------------------------------------------|

|                                                |

|                                                |

|                                                |

| Professor Yvan Labiche, Chair,                 |

| Department of Systems and Computer Engineering |

Ottawa-Carleton Institute for Electrical and Computer Engineering

Department of Systems and Computer Engineering

Carleton University

August, 2015

### Abstract

With the rising popularity of embedded systems came new challenges due to evergrowing market application demands, increasing complexity and widening productivity gap. To deal with these issues, model-driven development promotes a higher level of abstraction during design and uses models as the primary artifacts that guide the product development. In fact, the fundamental principle is to construct a model of a system and then transform it into the real system.

We focus on DEMES, a model-driven development methodology based on the Discrete Event System Specification (DEVS) — that defines a formal Modeling and Simulation framework for discrete event dynamic systems —, and especially the transition from simulated platform to execution platform, i.e. the embedded hardware. In this dissertation, we present bare-metal real-time executives that allow DEVS models to be executed on a target platform without the need of an operating system. This is particularly important for target platforms with limited resources. In addition to the real-time executives, we introduce a hardware abstract layer that supports several hardware peripheral libraries and fosters fast prototyping. We also illustrate the DEMES-driven development cycle with a particular case study: a line tracking robot application. Our contributions have resulted in a reduced footprint, increased performance and enhanced platform portability.

To my brother, David, for always lighting me up.

To my mother, Pascasie, for always lifting me up.

And above all, to God, The Father Almighty:

Ephesians 3:20-21.

# Acknowledgments

I thank Dr Gabriel Wainer whose invaluable advice and ongoing support helped through my graduate studies and research. One of my objectives in graduate school was to work with and learn from some of the best in the field, and I had this privilege under his supervision. The past two years have been both a challenging and rewarding experience.

I also thank the members of the Advanced Real-Time Simulation Laboratory for their help and comradeship.

# Table of Contents

| Al  | Abstract       |                                         |      |  |  |

|-----|----------------|-----------------------------------------|------|--|--|

| Ad  | cknov          | wledgments                              | V    |  |  |

| Га  | ıble o         | of Contents                             | vi   |  |  |

| Lis | ${ m st}$ of   | Tables                                  | x    |  |  |

| Li  | ${ m st}$ of   | Figures                                 | xi   |  |  |

| No  | omer           | nclature                                | ciii |  |  |

| 1   | $\mathbf{Int}$ | roduction                               | 1    |  |  |

|     | 1.1            | Overview                                | 1    |  |  |

|     | 1.2            | Contributions                           | 4    |  |  |

|     | 1.3            | Publications                            | 5    |  |  |

|     | 1.4            | Thesis Organization                     | 6    |  |  |

| 2   | Re             | view of the State of the Art            | 8    |  |  |

|     | 2.1            | The Evolution of Embedded System Design | 9    |  |  |

|     |                | 2.1.1 Traditional Design Methods        | 9    |  |  |

|     |                | 2.1.2 Model-Based Design                | 10   |  |  |

|     | 2.2            | Embedded System Design with DEVS        | 15   |  |  |

|   |                 | 2.2.1                                                                | DEMES                                       | 16                                                          |

|---|-----------------|----------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------|

|   |                 | 2.2.2                                                                | Model-Checking with DEMES                   | 19                                                          |

|   |                 | 2.2.3                                                                | Applicability to Low Level Applications     | 20                                                          |

|   | 2.3             | Embe                                                                 | dded CD++, a DEVS-based Tool                | 22                                                          |

|   |                 | 2.3.1                                                                | Features and Software Components Overview   | 23                                                          |

|   |                 | 2.3.2                                                                | PDEVS Model Definition                      | 25                                                          |

|   |                 | 2.3.3                                                                | PDEVS Model Execution                       | 28                                                          |

|   | 2.4             | From                                                                 | DEVS Models to Real-Time Execution          | 29                                                          |

|   | 2.5             | Hardw                                                                | vare Execution Platform                     | 35                                                          |

|   |                 | 2.5.1                                                                | ARM Microcontrollers                        | 35                                                          |

|   |                 | 2.5.2                                                                | Hardware Peripheral Libraries               | 37                                                          |

|   |                 | 2.5.3                                                                | MBED, Rapid Prototyping and IoT Platform    | 39                                                          |

|   |                 |                                                                      |                                             |                                                             |

| 3 | Pro             | oblem                                                                | Statement                                   | 41                                                          |

| 3 |                 |                                                                      | Statement sal Real-Time Executives          | <b>41 4</b>                                                 |

|   |                 | re-Met                                                               |                                             |                                                             |

|   | Ba              | re-Met                                                               | al Real-Time Executives                     | <b>4</b> 4                                                  |

|   | Ba              | re-Met<br>Execu<br>4.1.1                                             | tion on Bare-Metal                          | 46                                                          |

|   | <b>Ba</b> : 4.1 | re-Met<br>Execu<br>4.1.1                                             | cal Real-Time Executives tion on Bare-Metal | 44<br>46<br>48                                              |

|   | <b>Ba</b> : 4.1 | re-Met Execu 4.1.1 Embe                                              | tion on Bare-Metal                          | 44<br>46<br>48<br>49                                        |

|   | <b>Ba</b> : 4.1 | Execu<br>4.1.1<br>Embed<br>4.2.1                                     | tion on Bare-Metal                          | 44<br>46<br>48<br>49<br>50                                  |

|   | <b>Ba</b> : 4.1 | Execu<br>4.1.1<br>Embed<br>4.2.1<br>4.2.2                            | tion on Bare-Metal                          | 444<br>466<br>486<br>496<br>506<br>536                      |

|   | <b>Ba</b> : 4.1 | Execu<br>4.1.1<br>Embed<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4          | tion on Bare-Metal                          | 444<br>466<br>488<br>499<br>500<br>538                      |

|   | Bar 4.1 4.2     | Execu<br>4.1.1<br>Embed<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4          | tion on Bare-Metal                          | 444<br>466<br>488<br>499<br>500<br>535<br>588<br>599        |

|   | Bar 4.1 4.2     | Execu<br>4.1.1<br>Embed<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Embed | tion on Bare-Metal                          | 444<br>466<br>488<br>499<br>500<br>533<br>588<br>599<br>600 |

|                  |                        | 4.3.4 Execution Subsystem                                           | 69         |

|------------------|------------------------|---------------------------------------------------------------------|------------|

|                  |                        | 4.3.5 Ancillary Subsystem                                           | 72         |

|                  |                        | 4.3.6 Execution on the Target Platform                              | 72         |

| 5                | На                     | rdware Related Layers 7                                             | 74         |

|                  | 5.1                    | Hardware Peripheral Libraries Integration                           | 74         |

|                  | 5.2                    | MBED Integration                                                    | 76         |

|                  | 5.3                    | Summary                                                             | 78         |

| 6                | Ap                     | plying DEMES - A Case Study 7                                       | <b>7</b> 9 |

|                  | 6.1                    | System of Interest                                                  | 80         |

|                  | 6.2                    | DEVS Model Specification                                            | 81         |

|                  | 6.3                    | RTS Model Simulation - Virtual Environment Testing                  | 85         |

|                  | 6.4                    | Execution on the target platform with E-CD++                        | 92         |

|                  | 6.5                    | Execution on the target platform with E-CDBoost                     | 01         |

|                  | 6.6                    | Metrics Comparison: E-CD++ vs E-CDBoost                             | 08         |

|                  | 6.7                    | Moving from one target platform to another: The MBED advantage . 11 | 11         |

|                  | 6.8                    | Adding Connectivity: An IoT application                             | 12         |

| 7                | Co                     | nclusion and Future Work 11                                         | L4         |

| Li               | $\operatorname{st}$ of | References 11                                                       | L7         |

| $\mathbf{A}_{]}$ | ppen                   | dix A The DEVS Formalism 12                                         | 29         |

|                  | A.1                    | Formal Specification                                                | 31         |

| $\mathbf{A}_{]}$ | ppen                   | dix B Development boards and Software Development Flow 13           | 33         |

|                  | B.1                    | Development Boards                                                  | 33         |

|                  |                        | R 1 1 KFII's MCSTM32F200 Evaluation Roard 15                        | 22         |

|            | B.1.2 | STM32F429 Discovery Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 134 |

|------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | B.1.3 | NUCLEO-F411RE Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 134 |

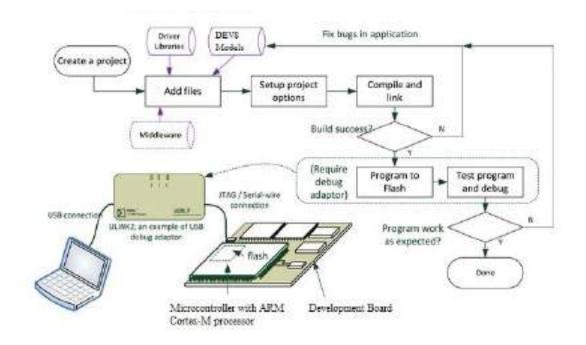

| B.2        | Embed | dded Software Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 135 |

| Appen      | dix C | Formal Specification of the Case Study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 137 |

| <b>- -</b> |       | The second of th |     |

| $O_1$      |       | 1 COMC 1 CO CO LITE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 127 |

| C.1        | Exam  | ple of a CM formal specification - The Control Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 197 |

# List of Tables

| 6.1 | Port Mapping            | 90  |

|-----|-------------------------|-----|

| 6.2 | CD++ Simulation Results | 91  |

| 6.3 | Overhead Evaluation     | 109 |

# List of Figures

| 2.1 | DEVS Transformation Graph                                                          | 16 |

|-----|------------------------------------------------------------------------------------|----|

| 2.2 | Discrete-Event Modeling of Embedded Systems (using DEVS)                           | 17 |

| 2.3 | E-CD++ Layers                                                                      | 22 |

| 2.4 | E-CD++ Software Components                                                         | 25 |

| 2.5 | Models and Execution Engines                                                       | 28 |

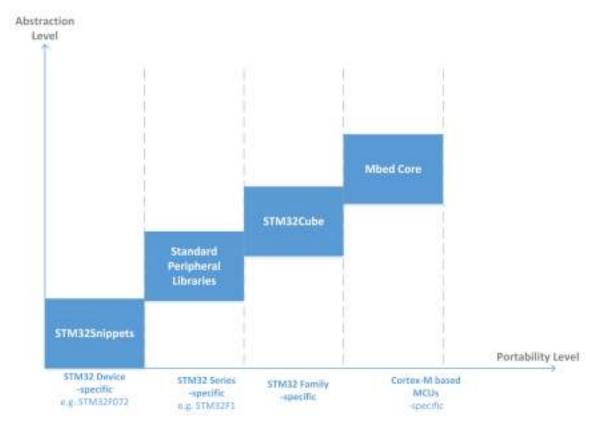

| 2.6 | $\operatorname{STMicroelectronics}$ Device Libraries - Abstraction and Portability | 38 |

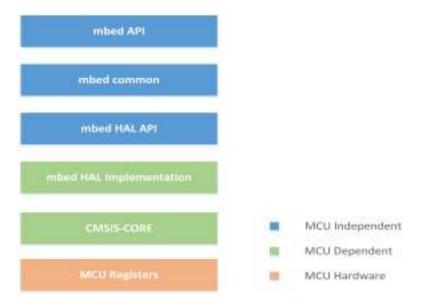

| 2.7 | MBED Design Overview                                                               | 40 |

| 4.1 | Bare-Metal E-CD++ Layers                                                           | 46 |

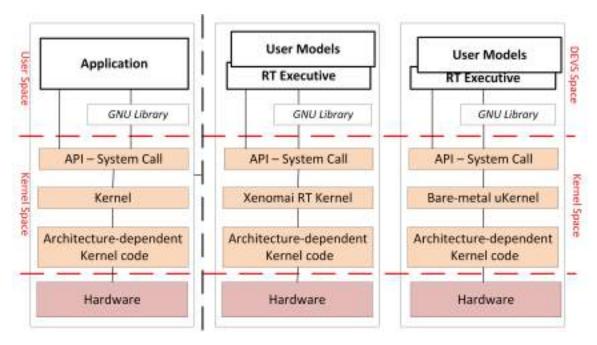

| 4.2 | RTOS vs Bare-Metal - An Overview                                                   | 47 |

| 4.3 | Software Components                                                                | 51 |

| 4.4 | Model and Processor Hierarchy with the Flattened Coordinator $$                    | 52 |

| 4.5 | Models and Processors                                                              | 54 |

| 4.6 | CDBoost, Software Components Overview                                              | 61 |

| 4.7 | Comparison of Communication Mechanisms                                             | 63 |

| 4.8 | Model Classes                                                                      | 68 |

| 4.9 | Execution Classes                                                                  | 70 |

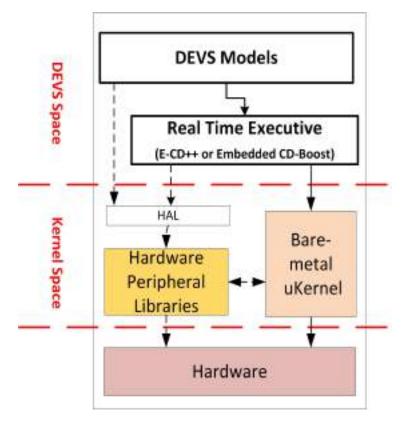

| 5.1 | Overview of the Bare-Metal Design                                                  | 75 |

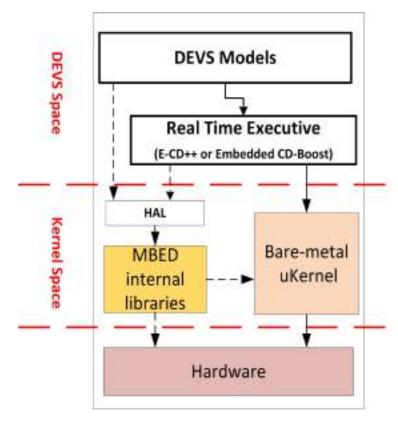

| 5.2 | Overview of the Bare-Metal Design with MBED                                        | 77 |

| 6.1 | DEMES-based Development Cycle                                                      | 79 |

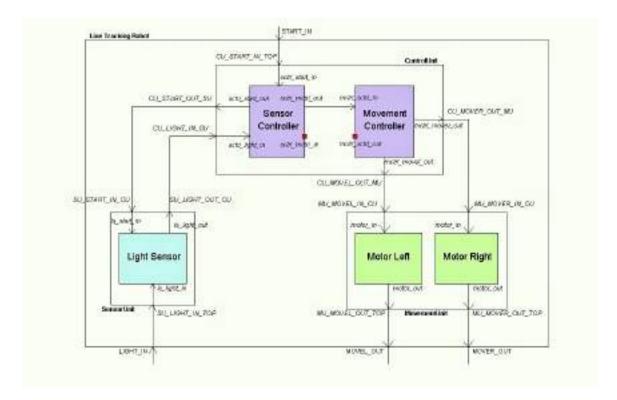

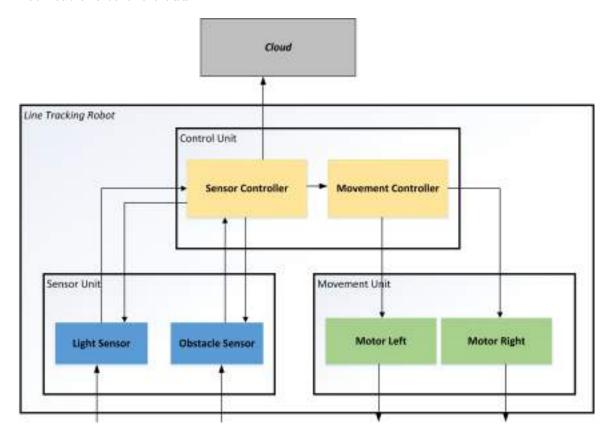

| 6.2 | Line Tracking Robot Model Hierarchy Diagram        | 82  |

|-----|----------------------------------------------------|-----|

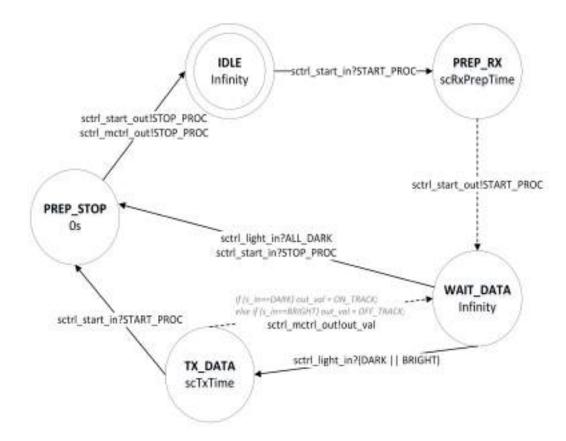

| 6.3 | Sensor Controller State Diagram                    | 84  |

| 6.4 | Modified Model Hierarchy Diagram                   | 112 |

| A.1 | Informal Definition of an Atomic Model             | 130 |

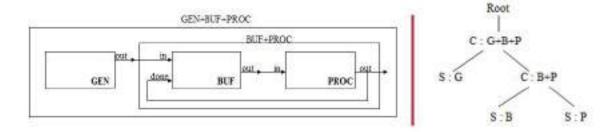

| A.2 | Generator-Buffer-Processor Hierarchical DEVS Model | 130 |

| B.1 | Simplified Software Development Flow               | 135 |

# Nomenclature

os

PDEVS RC

**RTES**

RTOS SPL

RTS

TA

UML UML-RT

VHDL

| $\overline{\mathbf{A}\mathbf{M}}$ | Atomic Model                                       |

|-----------------------------------|----------------------------------------------------|

| $\mathbf{API}$                    | Application Programming Interface                  |

| $\mathbf{CM}$                     | Coupled Model                                      |

| CMSIS                             | Cortex Microcontroller Software Interface Standard |

| DEMES                             | Discrete Event Methodology for Embedded Systems    |

| $\mathbf{DEVS}$                   | Discrete Event System Specification                |

| E-CD++                            | Embedded CD++                                      |

| E-CDBoost                         | Embedded CDBoost                                   |

| $\mathbf{ES}$                     | Embedded Systems                                   |

| $\mathbf{FSM}$                    | Finite State Machine                               |

| $\operatorname{GGAD}$             | General Graphical Advanced environment for DEVS    |

| GPIO                              | General Purpose Input/Output                       |

| HAL                               | Hardware Abstract Layer                            |

| IDE                               | Integrated Development Environment                 |

| $\mathbf{IoT}$                    | Internet of Things                                 |

| M&S                               | Modeling and Simulation                            |

| MCU                               | Microcontroller                                    |

| MDD                               | Model-Driven Development                           |

Operating System Parallel DEVS

Root Coordinator

Real-Time Systems

Timed Automata

UML for Real-Time

Real-Time Embedded Systems

Real-Time Operating System

Standard Peripheral Libraries

Universal Modeling Language

VHSIC Hardware Description Language

### Chapter 1

# Introduction

#### 1.1 Overview

Over the last few decades, embedded systems have ascended to a position of prevalence in the world. They are ubiquitous, diverse, and present in various industries such as aerospace, consumer electronics, defense, medical equipment and transportation. Embedded systems are generally defined as computing systems with tightly coupled hardware and software designed for a specific purpose. Real-Time Embedded Systems (RTES) [1], in particular, are not only subject to functional and logical correctness; they must also produce results within strict timing constraints. Missing these deadlines may lead to significant loss and in some cases catastrophic consequences. For instance, an airplane's flight controller must respond correctly within the required deadline, or the result could be serious injuries or death. Besides, RTES usually operate in limited resource environments, are required to have a small memory footprint, be low-cost solutions and have low power consumption.

In addition to dealing with timeliness requirements, RTES design needs to deal

with hardware/software partition, and cope with target systems increasing scalability and complexity. However, there is a real shortage of effective design and implementation practices. Indeed, besides the inherent challenges of embedded systems, the ever-increasing demands for new applications and technological advances have caused system complexities to grow at an exponential rate. Therefore, traditional design methodologies that conquer hardware and software are becoming infeasible and making software the most costly and least reliable part of RTES [2], with deficiencies originating from two main weak areas: the development cycle and system verification. Model-based development offers a promising solution by raising the level of abstraction and promoting models to principal artifacts that drives development. Yet, most model-based techniques do not have a formal foundation and struggle with system verification.

Formal methods, on the other hand, facilitate system verification since they have a strict mathematical foundation. However, most formal methods are hard to scale up [3], and they usually do not consider the physical environment that the embedded system controls. A practical solution to the above problems is the use of formal Modeling and Simulation (M&S) that combines the advantages of a simulation based approach with the rigor of a formal methodology [4].

The Discrete Event Methodology for Embedded Systems (DEMES) [5] [6] is one such approach. It is based on the Discrete Event System Specification (DEVS) [7], a formalism that decomposes complex systems into basic (behavioral) models, and composite (structural) models. DEVS is especially suitable for RTES since it provides a rich structural representation of components, and formal means for explicit time specification, which is essential to RTES. The formal part of DEVS allows model-checking essential to verifying of the system properties and building provably correct

software; while the M&S aspect is useful to handle complex system designs, interact with the physical environment models, and perform extensive testing in risk-free environments. In addition, DEMES has various advantages when compared to existing methodologies, especially because most model-based methods are semiformal and do not provide direct model continuity. Model continuity, in particular, refers to preserving the model specification as much as possible through the development process. With DEMES, models are consistently used through the entire development cycle. They are formally defined in the design/specification phase, used to perform model-checking, run simulations, and incrementally replaced with hardware surrogates. The original models end up being deployed on the target hardware where they act as controllers.

One particular component essential to models deployment on the embedded platform is the real-time executive. This latter executes original models on the particular

hardware. In this thesis, we present two DEVS-based kernels (composed of a real-time

executive, a microkernel, and a hardware abstraction layer) that run original models

directly on bare-metal. The objective is to be able to execute models directly on the

target system hardware without the need of an Operating System. The new real-time

execution engines provide functionalities similar to those of a real-time kernel, with

formal models operating as system processes. The development of these DEVS-based

real-time kernels involved the following tasks:

- 1. The development of stand-alone real-time executives able to run on bare-metal without the need of an intermediate operating system.

- 2. The design of a hardware abstraction layer that provides an interface between hardware specific components and general real-time executive components.

- 3. The integration of different tools (compiler, hardware debugger, embedded register viewer, etc.) into an IDE in order to effectively develop embedded baremetal applications.

- 4. The development of applications on top of the designed real-time execution engines.

#### 1.2 Contributions

In this thesis, we introduce two main contributions. The first is the development of DEVS-based real-time kernels that run on bare-metal. The second is the design of a hardware abstract layer that allows the execution engines to run on multiple microcontrollers.

The first contribution extends the applicability of M&S driven development by providing an OS independent DEVS execution engine. As a result, target devices such as low power microcontrollers where an operating system would require excessive resources, are now covered. Since RTES are pervasive and varied, we believe that solutions addressing current development shortcomings should be applicable to a wide range of devices in order to properly replace traditional techniques and be appealing to industry. We have designed DEVS-based kernels able to execute models on baremetal on different ARM-based boards without the need of middleware RTOS.

Two real-time executives were developed: one that reuses the components of E-CD++ [4] [8], an existing DEVS real-time executive that required the services of a Linux real-time kernel, and another one built around a new Parallel DEVS (PDEVS) sequential architecture [9]. This latter improves the performance of the executive by using a different message-passing concept between model execution engines.

The second main contribution is the design of a hardware abstraction layer that

provides a clear separation between the execution engine components and hardware specific services. We have designed a wrapper around the popular ARM MBED library [10] and integrated it with DEVS components in order to provide rapid prototyping and ease the development task. This library also allows the user to build Internet of Things (IoT) applications since MBED provides such a platform.

Finally, to illustrate and test the new real-time executives, we have built different applications among which is a line tracking robot. We present its development cycle, show how to build its application on the E-CD++ "legacy" version, as well as the new real-time executive. We also extend it with IoT capabilities to demonstrate the connectivity possibilities offered by the wrapper library.

#### 1.3 Publications

Three papers that describe our work have been either published or accepted for publication. Listed below, these papers present the design of the bare-metal execution engines, the design of the new simulator around a PDEVS sequential architecture, and the discrete event methodology for embedded systems.

- [11] Daniella Niyonkuru and Gabriel Wainer. "Towards a DEVS-based Operating System." In Proceedings of the 2015 ACM SIGSIM conference on Principles of advanced discrete simulation, London, UK, 2015.

- [9] Damian Vicino, Daniella Niyonkuru, Gabriel Wainer and Olivier Dalle.

"Sequential PDEVS Architecture." Proceedings of the 2015 Spring Simulation

Multiconference, Alexandria, VA, USA, 2015.

- [6] Daniella Niyonkuru and Gabriel Wainer. "Discrete Event Methodology for

Embedded Systems." Computing in Science & Engineering vol.17, no.5, pp.52-63, Sept.-Oct. 2015.

We are also currently working on the following journal articles:

- Daniella Niyonkuru and Gabriel Wainer. "A DEVS-Based Framework for Bare-Metal Embedded Applications." ACM Transactions on Modeling and Simulation, vol.(TBD): pp (TBD). (in progress)

- Daniella Niyonkuru and Gabriel Wainer. "Embedded CDBoost, Executing DEVS models in embedded systems." *Journal (TBD)*, vol.(TBD): pp (TBD). (in progress)

# 1.4 Thesis Organization

The first three chapters of this document are introductory in nature. Chapter 3 describes the scope and purpose of the project, referring to the previous research outlined in chapter 2.

Chapter 4 and 5 describe how the problem stated in chapter 3 was tackled. Chapter 4 describes the real-time executives. We start by introducing the common baremetal design in section 4.1. Section 4.2 is then related to the legacy version and outlines the software architecture and changes that were made to the existing design in order to remove existing Linux dependencies and allow bare-metal execution. Next, section 4.3 presents the real-time executive built around the new PDEVS Sequential Architecture. We explain the architecture and algorithms used to build this executive and the hardware integration process. After, chapter 5 presents the hardware related layers of our solution.

Chapter 6 studies extensively the development cycle of one of the applications we built: a line tracking robot. The system of interest, its model specification and simulation results are respectively presented in section 6.1, 6.2 and 6.3. Section 6.4 and 6.5 show how to build the system application on top of the new executives, and also assess their performances in 6.6. We describe in 6.7 how to port easily the built application from one platform to another. Finally, in section 6.8 is an Internet of Things (IoT) application that illustrates how devices can be easily interconnected using our platform.

The remaining chapter (7) concludes the dissertation and discusses future work.

### Chapter 2

# Review of the State of the Art

The traditional design approaches — where systems are directly designed at the low hardware or software levels — that are still used in most embedded system designs may be passable for small and medium sized systems; however, they are quickly becoming infeasible due to the ever-increasing complexity and new application market demands. Technology advances allow the integration of a rising number of components on a single chip; and Moores law that states that the number of transistors on a chip doubles every 18 months, still holds. In contrast, design methods improve at a much slower rate. This has resulted in a problem known as the productivity gap. Traditional methods cannot reduce the productivity gap; therefore, alternative approaches that can improve the quality, correctness, and modularity of systems by advancing the analysis and verification of properties as early as possible in the design flow are needed. Model-based techniques are today the most promising solution [12] to lessen the productivity gap and enhance the quality, correctness, and modularity of software systems and subsystems. In the following section, we will first revisit traditional design techniques and briefly describe how model-based design ascended. Afterwards, we will focus on model-based development.

### 2.1 The Evolution of Embedded System Design

#### 2.1.1 Traditional Design Methods

Since RTES are partly made of hardware and software, three important design aspects [13] have to be considered: the hardware design, the co-design of hardware and software, and the design of embedded software. Traditional design divides hardware and software design to conquer them separately. The design starts with an informal specification and then the decision is made on how functionality will be split between hardware and software [14]. Most embedded systems are designed from a register level description for the hardware part on one hand, and the embedded software code on the other hand [13]. The implementation is obtained using classical top-down methodology (synthesis and compilation) [15]. Two types of methodologies subsequently emerged from traditional design: language-based (software-centric) and synthetic-based (hardware-centric) methods. Language-based methods are centered on a specific programming language with a particular target run-time system. C and RT-Java are such examples. Synthesis-based originates from hardware design techniques. The development starts with a system description, usually structural, in a tractable fragment of a Hardware Description Language (HDL) like VHDL and Verilog [2]. Moreover, in this type of design, system architects may use C and C++ to describe the system at the system-level [16]. The C/C++ description is refined; and then translated into synthesizable HDL [17]. In a nutshell, traditional design methodologies trace their origins from either software or hardware traditions [2] but do not cover hardware-software co-design, and remain hard to verify against the initial specification. Consequently, long testing phases, error-prone products, and increased time to market are common. On the other hand, co-design [18] is essential in order to design complex applications since hardware components are diverse in heterogeneous systems and software-hardware interface should be handled earlier in the development cycle.

Methods centered on the semantics of abstract system description were later introduced in an attempt to gain independence from specific implementation platforms. They combine both language and synthesis-based techniques [19] in order to enable hardware/software co-design. Examples include SpecC, ImpulseC and SystemC [20]. The latter, for instance, combines synchronous hardware semantics with asynchronous execution mechanisms from C++. Although the previous co-design description languages were quite effective in system-level design, they were not enough.

Recent methodologies offer higher levels of abstraction and go beyond implementation platform independence. They are built on modeling languages such as the Unified Modeling Language (UML) [21] and the Architecture Analysis and Design Language (AADL) [22] [23]. These approaches are system architecture focused and model-centric, and therefore referred to as model-based techniques.

### 2.1.2 Model-Based Design

Model-Based Design (MBD) seeks to address heterogeneity, and targets system's increasing scalability and complexity early in the development cycle by using models to describe the system. Model-Based Engineering (MBE) [23] [24], more generally, refers to engineering practices where models are the central and indispensable artifacts throughout the products development cycle enclosing concept, development, deployment, operation and maintenance. MBE has emerged in a variety of guises including model-driven engineering(MDE) [25], model-driven development (MDD) [26], model-driven architecture (MDA) [27] [28] and model-centered development (MCD) [29]. In these processes, models drive the development process by going through a series of transformations - a more abstract model is refined into a less abstract one - until

they reach a final state where they are made executable either by code generation of model interpretation and ready to be deployed [30]. Model-driven development is therefore "simply the notion that we can construct a model of a system that we can then transform into the real thing" [31]. Examples of available commercial MBD tools are Matlab/Simulink [32], Rational Rhapsody [33], SCADE [34], Modelica [35] and NI LabView [36]. In the academic context, we can cite Ptolemy [37] and Metro II [38]. The previous modeling languages/tools have powerful capabilities and some have been successfully adopted in industry. However, most companies had to create or develop small domain-specific languages to compensate for the limitations of current techniques [39]. We will take a closer look at Matlab/Simulink and UML-based profiles to illustrate some of the existing shortcomings.

Simulink [32] is one of the most extensively used model-based toolchain. It is a block diagram environment for multidomain simulation and MBD. It supports simulation, automatic code generation, continuous test and verification of embedded systems [40]. Hierarchical subsystems are modeled with predefined library blocks. In particular, stateflow charts (discrete logic and model behavior definition) and simulink (for continuous dynamics) models are used to represent the system. To simulate the dynamic behavior of the modeled systems, Simulink provides fixed-step and variable-step ordinary differential equation solvers. Simulink models can also be configured to generate code in C/C++, HDL and PLC. The tool also supports model connection to hardware and hardware-in the-loop (HIL) simulation; Simulink provides built-in support for prototyping, testing, and running models on various target hardware (FPGA, low-cost embedded hardware such as Arduino and Lego Mindstorms). In addition, several toolboxes (e.g. Simulink Design Verifier, Simulink Verification and Validation, SystemTest, and Simulink Code Inspector) are available in Simulink for model checking, algorithm verification and validation according to certain industry standards (e.g.

DO-178D [41] and IEC 61508 [42]) [43].

Although the Mathworks development suite has powerful capabilities, its modeling languages lack formal and rigorous semantics for its models. Several initiatives such as [44], [45], [46] and [47] used different methods (communicating pushdown automata, tabular expressions) in an attempt to define formal semantics for the popular tool. However, only a subset of the modeling languages is covered, and models remain susceptible to interpretation errors that can be fatal for safety-critical embedded systems. Instead, SCADE (Safety Critical Application Development Environment) is sometimes preferred for safety-critical applications since it has formal pedigree (based on data flow graphs and finite state machine) and strong analysis capabilities. In addition to the absence of rigorous semantics, Simulink lacks a publicly accessible meta-model that would enable the integration with a larger metamodeling language such as UML [48].

UML, on the other hand, is already well established in software engineering and comes naturally as the de facto standard for MDD. A number of UML profiles have been proposed for modeling embedded systems, and include SysML (Systems Modeling Language) [49] and MARTE (Modeling and Analysis Real-Time and Embedded systems) [50]. SysML is for specifying, analyzing, designing, and verifying complex systems that may include hardware, software, information, personnel, procedures, and facilities; while MARTE supports specification of real-time and embedded systems [51]. In addition to functional design, this profile adds constructs to describe the hardware and software (e.g. OS services) resources and defines specific properties to enable designers to perform timing and power consumption analysis. MARTE is very general and supported by several tools. However, due to the complexity it has to support, MARTE is still a work in progress [12] subject to evaluation and extension proposals [52] [53] [54]. Alternatively, SysML and MARTE tend to be combined

because there is complementarity of technology coverage [55] [56]. Indeed, SysML supports modeling of a whole spectrum of diverse engineering technologies (e.g. mechanical, electrical, and hydraulic), and MARTE focuses primarily on real-time and embedded systems software and supporting platforms. Plus, the two can complement each other in terms of the level of abstraction they cover: the broader scope of SysML makes it a natural choice for representing systems at a higher level, whereas MARTE is better suited for finer grained modeling (e.g. the software aspects) [57]. However, because the two profile definitions are not yet fully synchronized with each other, combining them may lead to syntactic and semantic conflicts [57] [58]. The other main drawback of UML-based MDD is the gap between models and their execution. This step was particularly hindered by the lack of precise semantics that makes UML models hard to verify and can lead to model implementation inconsistencies. This lead to the adoption of fUML (foundational UML) [59] - the first precise operational and base semantics for a subset of UML encompassing most object-oriented and activity modeling- and ALF (Action Language for Foundational UML) [60] - a textual action language designed to specify executable fUML behaviors. Now, efforts such as in [61] are being directed towards defining formal semantics for UML profiles such as MARTE and SysML since they remain specified in prose (at best) and their semantic definitions stay informal. This considerably limits interest of profiles and their practical usability in a context in which engineers look for rapid prototyping. Other researchers, such as [62] [63] and [64], focus on providing mechanisms to further bridge the gap between model and code, and alleviate the burden associated with learning an extra action language, i.e. ALF.

Another approach used to tam heterogeneity in RTES design is the use of different Models of Computation (MoC) to cover a wide spectrum of domain. It is specifically referred to as Model-Integrated Development [65] and based on the idea that one

language cannot be enough to cover all domains and regroups several existing methods instead. Ptolemy II is a framework based on this concept. It is a structured and hierarchical approach, uses specific MoC that defines how computation takes place among a structure of computational components and supports discrete event, process networks (PN), dataflow (SDF), synchronous/reactive (SR) and continuous models. In Ptolemy II, real-time systems are modeled using DE; however Ptolemy II DE models don't have a formal specification and need to be transformed into a formal specification to enable model-checking. In [66], Real-Time Maude is integrated with Ptolemy II to enable formal verification. This way of integrating formal methods with MDE is also referred to as formal model engineering. This latter combines the convenience of using an informal but intuitive modeling language with formal verification. Nonetheless, useful information might be lost in the process of transforming informal models into formal models. Another alternative to preserve consistency would be to use methods that are natively formal and model-based.

Although model-based approaches handle well modern systems complexity and heterogeneity by raising the level of abstraction and allowing a hardware-software co-design, research remains to be done in the areas of development cycle — to reduce the model-to-execution gap — and model specification semantics — to enable formal verification. Indeed, direct model continuity should be supported and efficient model transformation provided to ensure that initial models are reused through the development cycle, maintain consistency, and offer a unified development framework. In addition to being effective at the high level (system description), model-based methods should also be effective at lower levels (implementation) and be applicable to devices with limited resources (e.g. memory) as well as large systems in order to compete with traditional methods. In terms of system verification, formal methods are needed to help with system verification and prove the system correctness.

To meet the previous considerations, a formal methodology that provides model continuity can be applied. In the following sections, we will introduce DEMES [5], a formal model-based development methodology based on Discrete-EVent System specifications (DEVS) [67]. DEVS is a well-defined formalism that is expressive, operates at a high level of specification, and can be used to represent both computing systems and the physical systems they control. DEMES offers a practical approach with a formal rigorous method in which models are consistently used throughout the development cycle.

# 2.2 Embedded System Design with DEVS

DEVS (Discrete EVent System Specification) is a Discrete Event Simulation formalism for modeling and simulating dynamic systems. The DEVS formalism decomposes complex system designs into basic (behavioral) models called atomic and composite (structural) models called coupled [67] (See Appendix A for details). It follows a precise rule set to define state changes of the modeled systems with regards to input events or time delay triggers. DEVS is particularly suitable for RTES as it provides a rich structural representation of components, and formal means for explicitly specifying their timing, which is central for real-time systems. It has been proven to be successful in different complex systems (e.g. [68], [69], [70], [71])

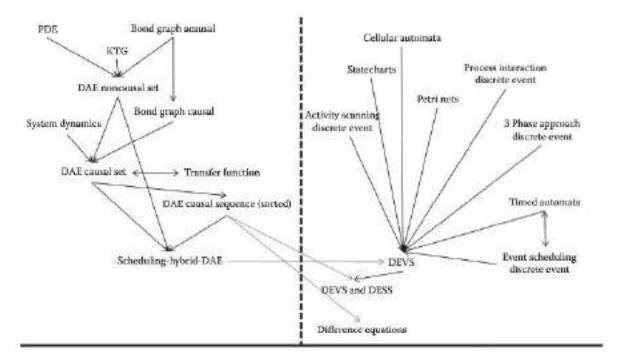

Besides, DEVS is the most general Discrete Event Formalism and many existing formalisms (e.g. Statecharts, Petri nets, Timed Automata ...) can be expressed as DEVS [5] (See figure 2.1 [72]) and allows existing system description translation(Verilog [73], VHDL [74] transformation to DEVS). Plus, DEVS theory does not only provide a rigorous methodology for model construction but also proposes an abstract simulation algorithm independent of the simulation mechanisms and the

Figure 2.1: DEVS Transformation Graph

underlying hardware and middleware.

#### 2.2.1 **DEMES**

DEMES focuses on bridging formal methods and M&S in order to analyze real-time systems and study their interaction with the physical environment while enabling original models to be part of the final product. This is achieved by using M&S for the initial stages, and replacing models incrementally with hardware surrogates and new software components without altering the original models. The transition can be done in incremental steps, incorporating models in the target environment after thorough testing in the simulated platform, allowing model reuse throughout the process.

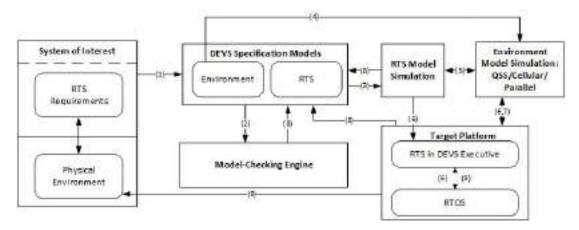

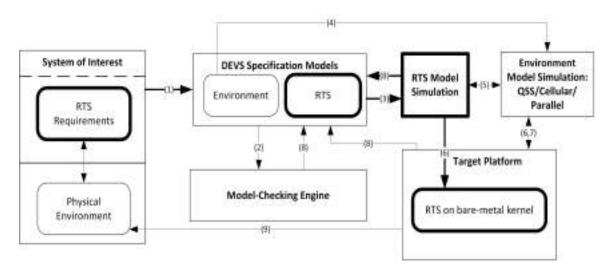

Figure 2.2 shows the architecture of the DEMES methodology. A designer starts

Figure 2.2: Discrete-Event Modeling of Embedded Systems (using DEVS)

(1) by modeling the System of Interest (a real time system and its environment) using formal specifications (DEVS or alternative techniques such as Statecharts, Modelica...). These models are converted into a DEVS representation, then transformed into Timed Automata, and verified using model-checking tools (2). In parallel with this formal verification phase (which can take a long time, in particular if state explosion happens during formal verification), the same models are used to test the components in a simulated DEVS environment (3). The physical environment can also be simulated (4) together with the RTS model under particular loads (5). Instead of obtaining general answers for all the possible cases (like those provided by modelchecking), we can simulate individual behaviors of the different sub models under specific conditions. In brief, we can study system properties analytically, and complement the proofs using simulation, which can also be used for hardware/software co-design (and later, for training). These tested submodels can then be deployed incrementally into the target platform (6). A real-time executive executes the models on the particular hardware. If the hardware is not readily available, the software components can still be developed incrementally and tested against a model of the hardware to verify viability and take early design decisions. As the design process evolves, both software and hardware models can be refined, progressively setting checkpoints in real prototypes. The executive allows to execute dynamic models and to schedule static and dynamic tasks. At this point, those parts that are still unverified in the formal and simulated environments are tested, increasing the confidence of the engineer into the implemented system. Most of the testing phase (7) can be done using simulation (with faster than real-time performance), even if the hardware is unavailable. Simulation provides a risk-free testing environment; and will be applicable in cases where real-life testing is impossible due to risks, ethical or practical issues. With DEMES, design changes are done incrementally in a spiral cycle (8), providing a consistent set of apparatus throughout the development cycle. The cycle ends with the RTS fully tested and every model deployed on the target platform.

This approach has various advantages when compared to existing methodologies. For instance, the methods discussed in section 2.1. were at most semi-formal and do not provide direct model continuity. In [75], the authors presented a comparison between DEVS and UML-RT showed that features such as time, scheduling and performance coded using UML constructions are not formally defined. Instead, formal modeling methods like DEVS provide sound syntax/semantics for structure, behavior, time representation and composition, which lend themselves to well-defined computation [76] [4]. Its expressiveness also allows to span multiple domain while remaining publicly accessible for integration with common standard modeling language such as UML [77] and some of its popular profiles [78]. DEVS has also been used in the past to bridge the gap between UML models and their execution such as in [79] and [80]. Moreover, the DEMES approach offers the following advantages [5] [81]:

Reliability: logical and timing correctness rely on DEVS system theoretical roots and sound mathematical theory;

- Model reuse: DEVS has well-defined concepts for coupling of components and hierarchical, modular model composition, supported by the formal concept of closure under coupling;

- Hybrid modeling: different methods can be used while keeping independence

at the level of the executive, using the most adequate technique on each part

of system architecture and reusing existing expertise, which allows knowledge

reuse;

- Process flexibility: hybrid modeling capabilities are transparent for the executive, which is defined by an abstract mechanism that is independent from the model itself;

- Verification and validation: the definition of experimental frames can be partially automated and formal verification is possible. Formal verification will be discussed in the next section.

#### 2.2.2 Model-Checking with DEMES

Model-checking allows the designer to verify models correctness and eventually produce formally correct software. Therefore, deployed systems will have a very high reliability as the formal verification permits error detection at the early stages of the design. When models used for M&S are formal, their correctness is verifiable. Another advantage of executable models is that they can be deployed to the target platform, thus providing the opportunity to use the controller model not only for simulations but also as the actual code executing on the target hardware. Hence, the verified model is itself the final implementation executing in real time. This prevents any new errors that might appear during transformation of the verified models into an implementation, therefore guaranteeing a high degree of correctness and reliability.

To verify DEVS models, we use a class of rational time-advance DEVS called RTA-DEVS [82] and then transform RTA-DEVS models into equivalent Timed Automata (TA) that are then used to formally verify the desired properties using the UPPAAL [83] [84] model checker tool. RTA-DEVS was introduced to provide the modeler with a formalism that is expressive and sufficient to model complex systems behavior while being verifiable through formal model-checking techniques. RTA-DEVS is a subclass of DEVS that restricts the time advance function to nonnegative rational numbers and the elapsed time in a state used in the external transition to be a nonnegative rational number. These restrictions mean that we will have nonnegative rational constants in guards of the resulting TA model and ensure termination of the reachability analysis algorithms implemented in UPPAAL.

[85] presents a case study using a controller for an e-puck robotic application and showed the practicality of our approach.

Apart from formal verification, the other essential aspect that new approaches ought to offer is model execution on the hardware target. From this point on, we will focus on this feature and explore existing solutions.

#### 2.2.3 Applicability to Low Level Applications

Recent research has focused on DEVS application to low-level applications commonly found in embedded systems consisting of computer hardware and real-time software. Existing DEVS based development environments for RTES include, for instance, DEVSJAVA [69], a Java DEVS-based simulator that supports high-level modeling; RTDEVS/CORBA [70] [86], a DEVS implementation based on real time CORBA communication middleware; and PowerDEVS [87] a tool for hybrid system modeling and real time simulation. In [76], the authors show how model continuity can be used in the design of dynamic distributed real-time systems. [88] presents

an application of the DEVS framework to the design and safety analysis of a RTES (a railroad crossing control system). In [71], an embedded control system model is built and its exhaustive verification temporal analysis done using Uppaal timed automata. In [89], model reuse and interoperability were shown by interfacing ECD++ and PowerDEVS. A System-On-Chip FPGA implementation of Embedded CD++ was presented in [90] and a M&S-based design of embedded controllers on network processors in [91]. The platform limitations remain significant compared to the traditional methods: In [76], [69], [70], [81] and [92] where implementation requires Java, the target hardware should be able to support the Java-implemented DEVS real-time execution environment. In [93] the authors presented a DEVS based real-time system on a TINI chip which has limited memory and processing ability. However, this requires Java Virtual Memory and Java class libraries availability on the chip. In [87], Linux RTAI kernel is required for PowerDEVS. The Embedded CD++ (E-CD++) developed by our team [8] relied on a variant of the Linux kernel. In [91], E-CD++ was embedded on the Core processor of an Intel IXP2400 Network Processor that runs RT Linux. Hence, it ran in the Linux User Space and requires Linux Kernel services. In [90], a configurable Linux kernel was downloaded to the SDRAM memory blocks on the AP1000 FPGA board. This dependency also included the use of the Xenomai real-time framework for Linux [94]. This latter provided hard real-time functionality to the Linux kernel. In the next section, E-CD++ software components will be presented and its implementation explained.

# 2.3 Embedded CD++, a DEVS-based Tool

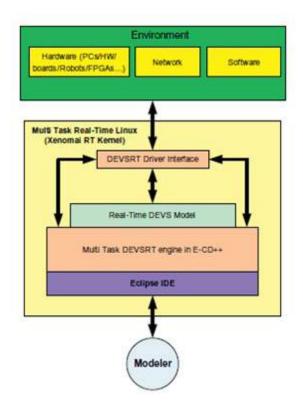

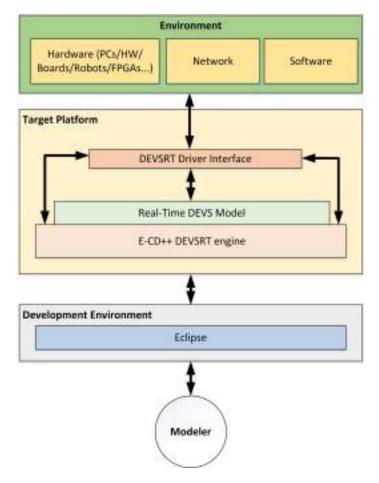

The DEVS formalism proposes a framework for model construction and defines an abstract simulation mechanism that is independent of the model itself. This mechanism provides a high-level implementation detail for the DEVS framework, and can be feasibly implemented by computer software. E-CD++ [8] is a real time implementation, based on the CD++ simulator [95] (a DEVS-based framework), and RT-CD++ [96] (an extension of CD++ for real-time simulation). E-CD++ supports modeling real-time systems by converting the CD++ virtual time-advance function to real-time, and provides an RT simulation platform for verification of such models. Figure 2.3 [4] illustrates the E-CD++ development framework. The embedded

Figure 2.3: E-CD++ Layers

platform with the external environment is shown in this layered approach representing the cross-platform development of models. The modeler defines models using a high-level DEVS language combined with C++ code if needed, which provides the application layer. These real-time models are then interpreted and executed by the DEVSRT (DEVS in Real-Time) engine [97].

#### 2.3.1 Features and Software Components Overview

To allow for direct replacement of models with external entities, the I/O ports of E-CD++ models implement the formal interfacing mechanism of DEVSRT in the Driver Interface layer. The underlying middleware is a real-time kernel and the runtime objects are imported to this platform as RT tasks. The E-CD++ execution engine uses the Xenomai real-time kernel [94] with multi-tasking services to implement DEVSRT. The user models and the driver objects were merged with the E-CD++ core objects; and the entire combination was compiled to produce an executable.

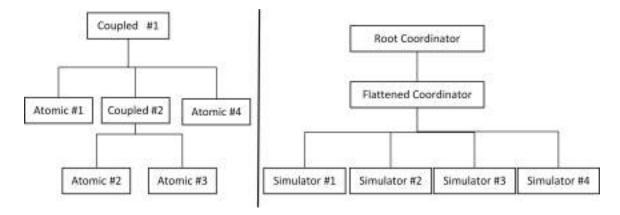

E-CD++ also include several features. The Eclipse IDE layer shown in figure 2.3 also allows for the graphical development of models. Through the IDE, the Generic Graphical Advanced environment for DEVS modeling and simulation (GGAD) [8] allows the developer to use a graph-based representation to specify models hierarchy, interconnections and behaviors to automate model generation. At the execution engine level, various features have been implemented in order to improve the software including DEVSRT simulation algorithms, a Flattened Coordinator technique and a Time Interval function. The simulation algorithms allow correct handling of simultaneous events through the implementation of a messaging behavior for model interaction (See next section for details). The Flattened Coordinator technique improves the efficiency of the DEVSRT messaging behavior through the removal of superfluous messages that are generated for communication between coupled models.

Finally, the Time Interval function enforces real-time constraints through the use of wall-clock time advancement and execution deadline checking.

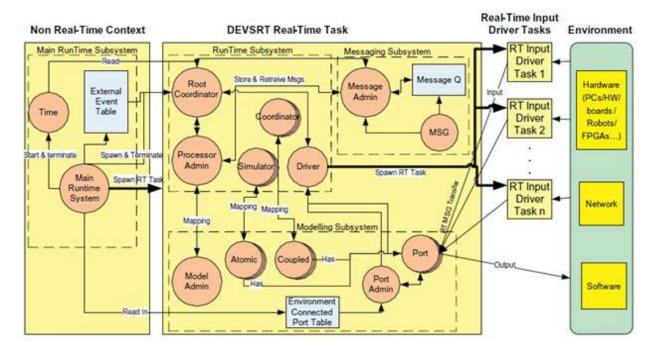

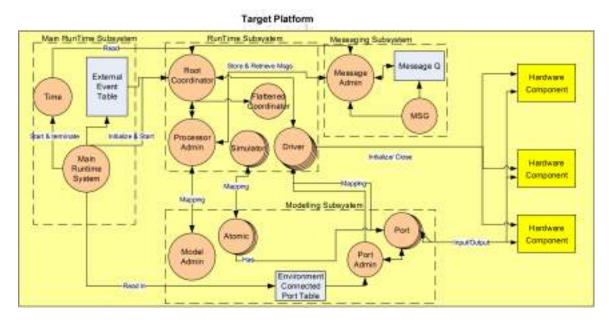

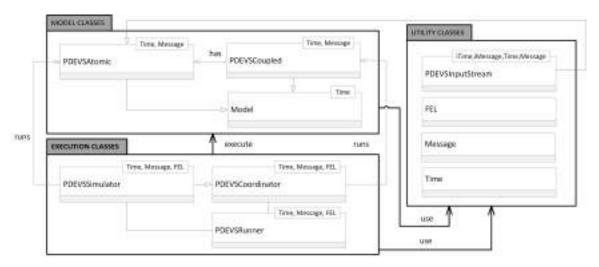

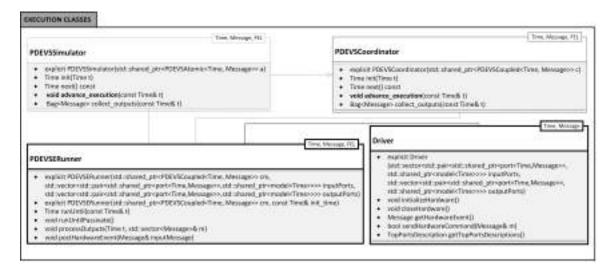

E-CD++ has four main components [Figure 2.4]: the Main Runtime System, the Modeling Subsystem, the Runtime Subsystem and the Messaging Subsystem [4]. The Main Runtime System manages the overall aspects of the real-time execution and provides timing functions with microsecond precision. The Main Runtime System is the first object that is created in non-real-time context, and it launches the Runtime Subsystem [4] [8]. In general, the Main Runtime System first register Atomic component objects, then the Top coupled component ports that are connected to the external environment, reads in the external events (from an existing event-file) and builds an external event table. After that, the Main Runtime System reads in the model-file and builds the model hierarchy. Finally, it spawns the main real-time task in which the Root Coordinator (RC) is created to start the DEVSRT execution cycle.

The Runtime Subsystem consists of Simulators, Coordinators, and the Processor Admin. In E-CD++, simulators are run-time engines that correspond to atomic components, and they perform the main job of executing the internal transition and output function after receiving the proper messages. Coordinators are coupled models execution engines. The RC is a special Coordinator that manages the real-time event scheduling. It initializes the global Driver object which launches the real-time input driver tasks (which are associated with input ports of the Top coupled component in the DEVS model hierarchy) declared by the user.

The Modeling subsystem is generated in order to define the atomic and coupled models, as well as the relationships between them. For each of these models, a processor is defined within the Runtime Subsystem in order to manage the behavior of the model and drive the execution. The Messaging subsystem provides the PDEVS

Figure 2.4: E-CD++ Software Components

behavior [8]. PDEVS models as well as their execution are explained in the following section.

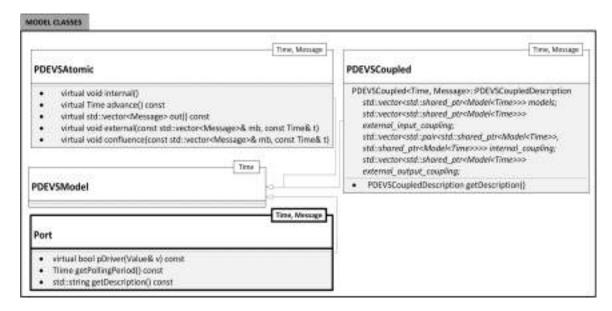

#### 2.3.2 PDEVS Model Definition

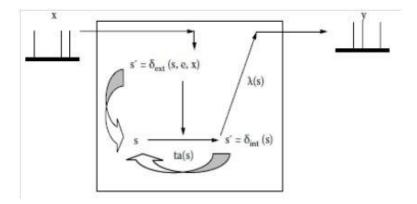

The original DEVS formalism was extended to resolve serialization constraints and allow simultaneous events, defining what is called Parallel DEVS (PDEVS) [98]. As with classic DEVS (Appendix A), systems are described using states that change upon the reception of an input event or the expiration of a delay. To tackle the complexity of the system, PDEVS decomposes the system into behavioral models called *atomic models* and structural models called *coupled models* similar to classic DEVS. Two types of events - internal and external events - influence the behavior of atomic models and cause state changes. When an external event occurs, an external transition function is executed and determines the new state of the model. In the

absence of external events, the model stays in a state s for a certain time ta(s). When ta(s) expires, e.g. an internal event occurs, the model outputs a value and then changes to a new state given by an internal transition function. In classic DEVS, whenever two models are scheduled for state transitions at the same time, one of the models is chosen according to a select function provided in the coupled model specification. This function provides a tie-breaking mechanism by defining an ordering over all the components so that only one model is picked in the case of simultaneous events. Hence, collision behaviors cannot be represented properly and serialization is introduced in the execution of components. With PDEVS, atomic models provide an additional confluent function specifying what to do under such collisions, and it uses bags of events for receiving inputs and collecting outputs. Therefore, external and output functions handle bags of events allowing simultaneous processing of multiple events and eliminating the necessity for the select tie-breaking function used in classic DEVS.

A parallel atomic DEVS is specified as follows [98]:

$$M = \{X, Y, S, \delta_{ext}, \delta_{int}, \delta_{con}, \lambda, ta\}$$

Where X is the set of input events, S the set of sequential states, Y is the set of output events,  $\delta_{ext}$  is the external transition function,  $\delta_{int}$  is the internal transition function,  $\delta_{con}$  is the confluent function,  $\lambda$  is the output function and ta is the time advance function. In this specification, the confluent transition function  $s' = \delta_{con}(s,e,x)$  computes the next state using the current state s, the elapsed time e and the input events x when the internal and external events occur simultaneously. The rest of the PDEVS specification follows the classic DEVS specification [7].

A parallel coupled DEVS is specified as follows [98]:

$$CM = \{X, Y, D, \{M_i\}, \{I_i\}, \{Z_{i,j}\}\}\$$

Where X is the set of input events, Y is the set of output events, D is the set of the component names,  $M_i$  is the DEVS system of component name  $i \in D$ ,  $I_i$  is the influences of i for each  $i \in D$ , and  $Z_{i,j}$  defines the i-to-j output translation for each j in  $I_i$ . The whole CM specification follows the classic coupled DEVS specification except for the Select function.

The DEVSRT [4] formalism, used in E-CD++, is built on top of PDEVS and associates a deadline to each atomic model since meeting deadlines is crucial in real-time systems. A DEVSRT atomic model is formally defined as:

$$MRT = \langle X, S, Y, \delta_{ext}, \delta_{int}, \delta_{con}, \lambda, ta, d \rangle,$$

Where:

- X, S, Y,  $\delta_{ext}$ ,  $\delta_{int}$ ,  $\delta_{con}$  and  $\lambda$  are the same as PDEVS.

- ta:  $S \to R_{0,\infty}^+$ , time advance function which works with physical clock of the system

- ullet d:  $S \to R_{0,\infty}^+$ , is the relative deadline of each state for output production.

The coupled model definition is the same as PDEVS. Since DEVSRT is consistent with the PDEVS formalism, PDEVS models can be reused for RTES.

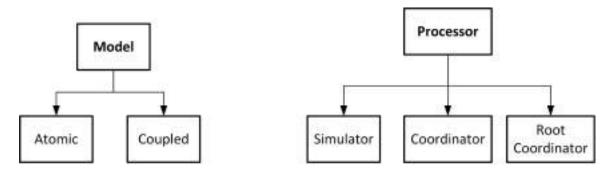

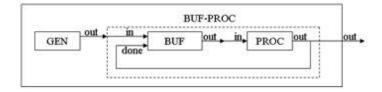

#### 2.3.3 PDEVS Model Execution

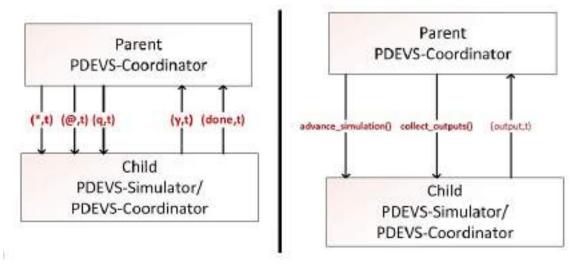

Each DEVS specification can be executed by an abstract simulator that defines the execution semantics of the models. The PDEVS abstract simulation algorithms uses two kinds of components: Simulators (in charge of Atomic models), and Coordinators (in charge of Coupled models), using a one to one mapping between models and simulation components. Simulators are the engines that invoke the model transition functions ( $\delta_{int}$ ,  $\delta_{ext}$ ,  $\delta_{con}$ , ta,  $\lambda$ ); Figure 2.5 shows a coupled model example and its corresponding execution tree. Atomic models are associated with simulators (denoted by "S") while coupled models are linked to coordinators (indicated by "C"). For instance, S:B is the simulator calling the buffer (BUF)  $\delta_{int}$  if an internal transition is needed. Coordinators on the other hand are in charge of event routing and hierarchical scheduling. C:B+P for instance will route events to S:B and S:P.

Figure 2.5: Models and Execution Engines

Simulation/Execution advances through message exchange. Five types of messages are used: three for synchronization (i.e. \*,@,done) and two for content(q,y).

Synchronization messages and the actions triggered by each message are shown below:

- (@, t): Output execution

- (\*, t ) : State transition

• (done, t): End of action

For content messages,

• (y,t): Output event

$\bullet$  ( q , t ) : External event

Parents and children communicate via this message passing mechanism. The abstract simulator also provide a set of algorithms of the coordinators, and simulators that specify how each simulation engine reacts upon the reception of those messages. The simulators and coordinators implemented in E-CD++ communicate via this message passing mechanism, and follow the abstract algorithms explained in the next section.